# **Chapter 5 General register file(GRF)**

### 5.1 Overview

The general register file will be used to do static set by software, which is composed of many registers for system control.

#### 5.1.1 Features

The function of general register file is:

- IOMUX control

- Control the state of GPIO in power-down mode

- GPIO PAD pull down and pull up control

- Used for common system control

- Used to record the system state

# **5.2 GRF Register Description**

# **5.2.1 Register Summary**

| Name                  | Offset | Size | Reset<br>Value | Description                 |

|-----------------------|--------|------|----------------|-----------------------------|

| GRF_GPIO0A_IOMUX      | 0x00a8 | W    | 0x00000000     | GPIO0A iomux control        |

| GRF_GPIO0B_IOMUX      | 0x00ac | W    | 0x00000000     | GPIO0B iomux control        |

| GRF_GPIO0C_IOMUX      | 0x00b0 | W    | 0x00000000     | GPIO0C iomux control        |

| GRF_GPIO0D_IOMUX      | 0x00b4 | W    | 0x00000000     | GPIO0D iomux control        |

| GRF_GPIO1A_IOMUX      | 0x00b8 | W    | 0x00000c00     | GPIO1A iomux control        |

| GRF_GPIO1B_IOMUX      | 0x00bc | W    | 0x00000030     | GPIO1B iomux control        |

| GRF_GPIO1C_IOMUX      | 0x00c0 | W    | 0x00000000     | GPIO1C iomux control        |

| GRF_GPIO1D_IOMUX      | 0x00c4 | W    | 0x00000000     | GPIO1D iomux control        |

| GRF_GPIO2A_IOMUX      | 0x00c8 | W    | 0x00000000     | GPIO2A iomux control        |

| GRF_GPIO2B_IOMUX      | 0x00cc | W    | 0x00000000     | GPIO2B iomux control        |

| GRF_GPIO2C_IOMUX      | 0x00d0 | W    | 0x00000000     | GPIO2C iomux control        |

| GRF_GPIO2D_IOMUX      | 0x00d4 | W    | 0x00000000     | GPIO2D iomux control        |

| GRF_GPIO3A_IOMUX      | 0x00d8 | W    | 0x00000000     | GPIO3A iomux control        |

| GRF_GPIO3B_IOMUX      | 0x00dc | W    | 0x00000000     | GPIO3B iomux control        |

| GRF_GPIO3C_IOMUX      | 0x00e0 | W    | 0x00000000     | GPIO3D iomux control        |

| GRF_GPIO3D_IOMUX      | 0x00e4 | W    | 0x00000000     | GPIO3D iomux control        |

| GRF_GPIO2C_IOMUX<br>2 | 0x00e8 | W    | 0×00000000     | GPIO2C iomux control        |

| GRF_CIF_IOMUX         | 0x00ec | W    | 0x00000000     | CIF iomux control           |

| GRF_CIF_IOMUX1        | 0x00f0 | W    | 0x00000000     | CIF iomux control register1 |

| GRF_GPIO_DS           | 0x0100 | W    | 0x00000000     | GPIO DS control             |

| GRF GPIOOL PULL       | 0x0118 | ۱۸/  | 0x00000000     | GPIO0A / GPIO0B pull        |

| GKI _GF100L_F0LL      | 000110 | VV   | 0x0000000      | up/down control             |

| GRF GPIO0H PULL       | 0x011c | ۱۸/  | 0×00000000     | GPIO0C / GPIO0D pull        |

| GKI _GI 10011_1 022   | OXOTIC | ٧٧   | 020000000      | up/aown control             |

| GRF_GPIO1L_PULL       | 0x0120 | ۱۸/  | 0x00000000     | GPIO0A / GPIO0B pull        |

|                       | 070120 | **   |                | up/uowii control            |

| GRF GPIO1H PULL       | 0x0124 | w    | 0×00000000     | GPIO1C / GPIO1D pull        |

|                       | JAGIZT | • •  | 2.000000       | up/down control             |

| Name             | Offset  | Size | Reset<br>Value | Description                          |

|------------------|---------|------|----------------|--------------------------------------|

| GRF_GPIO2L_PULL  | 0x0128  | W    | 0x00000000     | GPIO2A / GPIO2B pull                 |

|                  |         | <br> |                | GPIO2C / GPIO2D pull                 |

| GRF_GPIO2H_PULL  | 0x012c  | W    | 0x00000000     | up/down control                      |

| GRF_GPIO3L_PULL  | 0x0130  | W    | 0x00000000     | GPIO3A / GPIO3B pull up/down control |

| GRF_GPIO3H_PULL  | 0x0134  | ١٨/  | 0x00000000     | CDIO2C / CDIO2D mull                 |

|                  |         |      |                | up/down control                      |

| GRF_ACODEC_CON   | 0x013c  |      |                | SoC control register                 |

| GRF_SOC_CON0     | 0x0140  |      |                | SoC control register                 |

| GRF_SOC_CON1     | 0x0144  | -    |                | SoC control register                 |

| GRF_SOC_CON2     | 0x0148  | -    |                | SoC control register                 |

| GRF_SOC_STATUS0  | 0x014c  | -    |                | SoC status register                  |

| GRF_LVDS_CON0    | 0x0150  |      |                | LVDS control register                |

| GRF_DMAC_CON0    | 0x015c  |      |                | DMAC control register                |

| GRF_DMAC_CON1    | 0x0160  |      |                | DMAC control register                |

| GRF_DMAC_CON2    | 0x0164  | -    |                | DMAC control register                |

| GRF_MAC_CON0     | 0x0168  |      |                | GMAC control register0               |

| GRF_MAC_CON1     | 0x016c  |      |                | GMAC control register1               |

| GRF_TVE_CON      | 0x0170  | W    | 0x00000000     | TV encoder control register          |

| GRF_UOC0_CON0    | 0x017c  | W    | 0x00000000     | OTG control register                 |

| GRF_UOC1_CON1    | 0x0184  | W    | 0x00000000     | usb host control register            |

| GRF_UOC1_CON2    | 0x0188  | W    | 0x0000c820     | UOC1 control register 2              |

| GRF_UOC1_CON3    | 0x018c  | W    | 0x00000b40     | UOC1 control register 3              |

| GRF_UOC1_CON4    | 0x0190  | W    | 0x0000001c     | USB HOST 2.0 control register        |

| GRF_UOC1_CON5    | 0x0194  | W    | 0×00000000     | USB HOST 2 0 control                 |

| GRF DDRC STAT    | 0x019c  | W    | 0x00000000     | DDRC status                          |

| GRF_SOC_STATUS1  | 0x01a4  |      |                | SoC status register                  |

| GRF CPU CON0     | 0x01a8  |      |                | CPU control register                 |

| GRF CPU CON1     | 0x01ac  |      |                | CPU control register                 |

| GRF CPU CON2     | 0x01b0  |      |                | CPU control register                 |

| GRF CPU CON3     | 0x01b4  |      |                | CPU control register                 |

| GRF_CPU_STATUS0  | 0x01c0  | -    |                | CPU status register                  |

| GRF_CPU_STATUS1  | 0x01c4  |      |                | CPU status register                  |

| GRF OS REGO      | 0x01c8  |      |                | software OS register                 |

| GRF_OS_REG1      | 0x01cc  |      |                | software OS register                 |

| GRF_OS_REG2      | 0x01d0  |      |                | software OS register                 |

| GRF_OS_REG3      | 0x01d4  |      |                | software OS register                 |

| GRF OS REG4      | 0x01d8  |      |                | software OS register                 |

| GRF_OS_REG5      | 0x01dc  |      |                | software OS register                 |

| GRF_OS_REG6      | 0x01dc  | -    |                | software OS register                 |

| GRF_OS_REG7      | 0x01e0  |      |                | software OS register                 |

| GRF_PVTM_CON0    | 0x01e4  |      |                | PVTM control register                |

|                  |         |      |                |                                      |

| GRF_PVTM_CON1    | 0x0204  |      |                | PVTM control register                |

| GRF_PVTM_CON2    | 0x0208  |      |                | PVTM control register                |

| GRF_PVTM_CON3    | 0x020c  |      |                | PVTM control register                |

| GRF_PVTM_STATUS0 | 10X0510 | VV   | UXUUUUUUUU     | PVTM status register0                |

| Name                 | Offset | Size | Reset      | Description                         |

|----------------------|--------|------|------------|-------------------------------------|

| GRF PVTM STATUS1     | 0v0214 | ۱۸/  | Value      | PVTM status register1               |

| GRF_PVTM_STATUS2     |        |      |            | PVTM status register2               |

| GRF_PVTM_STATUS3     |        |      |            | PVTM status register3               |

| GRF_DFI_WRNUM        | 0x0210 |      |            | DFI write number register           |

| GRF DFI RDNUM        | 0x0224 |      |            | DFI read number register            |

| GRF_DFI_ACTNUM       | 0x0228 |      |            | DFI active number register          |

| GRF DFI TIMERVAL     | 0x022c |      |            | DFI work time                       |

| GRF NIF FIFO0        | 0x0230 |      |            | NIF status register                 |

| GRF NIF FIFO1        | 0x0234 |      |            | NIF status register                 |

| GRF_NIF_FIFO2        | 0x0238 | W    |            | NIF status register                 |

| GRF_NIF_FIFO3        | 0x023c | W    |            | NIF status register                 |

| GRF_USBPHY0_CON 0    | 0x0280 | W    | 0x00008618 | usbphy control register             |

| GRF_USBPHY0_CON 1    | 0x0284 | W    | 0x0000e007 | usbphy control register             |

| GRF_USBPHY0_CON 2    | 0x0288 | W    | 0x000082aa | usbphy control register             |

| GRF_USBPHY0_CON 3    | 0x028c | W    | 0×00000200 | usbphy control register             |

| GRF_USBPHY0_CON 4    | 0x0290 | W    | 0×00000002 | usbphy control register             |

| GRF_USBPHY0_CON<br>5 | 0x0294 | W    | 0×00000000 | usbphy control register             |

| GRF_USBPHY0_CON 6    | 0x0298 | W    | 0x00000004 | usbphy control register             |

| GRF_USBPHY0_CON 7    | 0x029c | W    | 0x000068c0 | usbphy control register             |

| GRF_USBPHY1_CON 0    | 0x02a0 | w    | 0x00008618 | usbphy control register             |

| GRF_USBPHY1_CON 1    | 0x02a4 | W    | 0x0000e007 | usbphy control register             |

| GRF_USBPHY1_CON 2    | 0x02a8 | W    | 0x000082aa | usbphy control register             |

| GRF_USBPHY1_CON 3    | 0x02ac | W    | 0×00000200 | usbphy control register             |

| GRF_USBPHY1_CON 4    | 0x02b0 | W    | 0×00000002 | usbphy control register             |

| GRF_USBPHY1_CON<br>5 | 0x02b4 | W    | 0×00000000 | usbphy control register             |

| GRF_USBPHY1_CON<br>6 | 0x02b8 | W    | 0x00000004 | usbphy control register             |

| GRF_USBPHY1_CON<br>7 | 0x02bc | W    |            | usbphy control register             |

| GRF_UOC_STATUS0      | 0x02c0 | W    | 0x0000000  | SoC status register 0               |

| GRF_CHIP_TAG         | 0x0300 | W    | 0x0000293c | chip tag register                   |

| GRF_MMC_DET_CNT      | 0x0304 |      | 0x0000fdb9 | mmc0 detect filter counter register |

| GRF_EFUSE_PRG_EN     | 0x037c | W    | 0x00000000 | efuse program register              |

# **5.2.2 Detailed Register Description**

### **GRF\_GPIO0A\_IOMUX**

Address: Operational Base + offset (0x00a8)

GPIO0A iomux control

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | wo   | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software. When bit 31=1, bit 15 can be written by software; When bit 31=0, bit 15 cannot be written by software; |

| 15:14 | RW   | 0×0         | gpio0a7_sel<br>GPIO0A[7] iomux select<br>01: i2c3_sda<br>10: hdmi_ddcsda<br>00: gpio                                                                                                                                                                                                                                                                                                                 |

| 13:12 | RW   | 0x0         | gpio0a6_sel GPIO0A[6] iomux select 01: i2c3_scl 10: hdmi_ddcscl 00: gpio                                                                                                                                                                                                                                                                                                                             |

| 11:8  | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                             |

| 7:6   | RW   | 0×0         | gpio0a3_sel GPIO0A[3] iomux select 01: i2c1_sda 10: mmc1_cmd 00: gpio                                                                                                                                                                                                                                                                                                                                |

| 5     | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                             |

| 4     | RW   | 0×0         | gpio0a2_sel GPIO0A[2] iomux select 1: i2c1_scl 0: gpio                                                                                                                                                                                                                                                                                                                                               |

| 3     | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                             |

| 2     | RW   | 0×0         | gpio0a1_sel<br>GPIO0A[1] iomux select<br>1: i2c0_sda<br>0: gpio                                                                                                                                                                                                                                                                                                                                      |

| 1     | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                             |

| Bit | Attr | Reset Value | Description                                            |

|-----|------|-------------|--------------------------------------------------------|

| 0   | RW   | 0x0         | gpio0a0_sel GPIO0A[0] iomux select 1: i2c0_scl 0: gpio |

# **GRF\_GPIO0B\_IOMUX**

Address: Operational Base + offset (0x00ac)

GPIO0B iomux control

| Bit   | Attr     | Reset Value | Description                                                                                                                                                                                                                                                                                                                                        |

|-------|----------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | wo       | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software. When bit 31=0, bit 15 cannot be written by software; |

| 15    | RO       | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                           |

| 14    | RW       | 0x0         | gpio0b7_sel GPIO0B[7] iomux select 1: hdmi_hotplugin 0: gpio                                                                                                                                                                                                                                                                                       |

| 13:12 | RW       | 0x0         | gpio0b6_sel GPIO0B[6] iomux select 01:i2s_sdi 10: spi_csn0 00: gpio                                                                                                                                                                                                                                                                                |

| 11:10 | RW       | 0x0         | gpio0b5_sel GPIO0B[5] iomux select 01:i2s_sdo 10: spi_rxd 00: gpio                                                                                                                                                                                                                                                                                 |

| 8     | RO<br>RW | 0x0<br>0x0  | reserved gpio0b4_sel GPIO0B[4] iomux select 1: i2s_lrcktx 0: gpio                                                                                                                                                                                                                                                                                  |

| 7:6   | RW       | 0×0         | gpio0b3_sel GPIO0B[3] iomux select 01:i2s_lrckrx 10: spi_txd 00: gpio                                                                                                                                                                                                                                                                              |

| 5:4   | RO       | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                           |

| Bit | Attr | Reset Value | Description                                                         |

|-----|------|-------------|---------------------------------------------------------------------|

| 3:2 | RW   | 0x0         | gpio0b1_sel GPIO0B[1] iomux select 01:i2s_sclk 10: spi_clk 00: gpio |

| 1   | RO   | 0x0         | reserved                                                            |

| 0   | RW   | 0x0         | gpio0b0_sel GPIO0B[0] iomux select 1: i2s_mclk 0: gpio              |

**GRF\_GPIOOC\_IOMUX**Address: Operational Base + offset (0x00b0)

GPIO0C iomux control

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | WO   | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software. When bit 31=1, bit 15 can be written by software; When bit 31=0, bit 15 cannot be written by software; |

| 15    | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                             |

| 14    | RW   | 0×0         | <pre>gpio0c7_sel GPIO0C[7] iomux select 1: nand_cs1 0: gpio</pre>                                                                                                                                                                                                                                                                                                                                    |

| 13:9  | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                             |

| 8     | RW   | 0×0         | gpio0c4_sel GPIO0C[4] iomux select 1: hdmi_cecsda 0: gpio                                                                                                                                                                                                                                                                                                                                            |

| 7:4   | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                             |

| 3:2   | RW   | 0×0         | gpio0c1_sel GPIO0C[1] iomux select 01: sc_io 10: uart0_rstn 00: gpio                                                                                                                                                                                                                                                                                                                                 |

| 1:0   | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                             |

# GRF\_GPIO0D\_IOMUX

Address: Operational Base + offset (0x00b4)

#### GPIO0D iomux control

| Bit         | Attr     | Reset Value | Description                                                                                                                                                                                                                                                                                                                              |

|-------------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16       | WO       | 0x0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software. When bit 31=0, bit 15 cannot be written by |

| 15.12       | DO.      | 00          | software;                                                                                                                                                                                                                                                                                                                                |

| 15:13<br>12 | RO<br>RW | 0x0<br>0x0  | reserved gpio0d6_sel GPIO0D[6] iomux select 1: mmc1_pwren 0: gpio                                                                                                                                                                                                                                                                        |

| 11:9        | RO       | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                 |

| 8           | RW       | 0x0         | gpio0d4_sel GPIO0D[4] iomux select 1:pwm_2 0: gpio                                                                                                                                                                                                                                                                                       |

| 7           | RO       | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                 |

| 6           | RW       | 0x0         | gpio0d3_sel GPIO0D[3] iomux select 1: pwm_1 0: gpio                                                                                                                                                                                                                                                                                      |

| 5           | RO       | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                 |

| 4           | RW       | 0x0         | gpio0d2_sel GPIO0D[2] iomux select 1: pwm_0 0: gpio                                                                                                                                                                                                                                                                                      |

| 3           | RO       | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                 |

| 2           | RW       | 0x0         | gpio0d1_sel GPIO0D[1] iomux select 1: uart2_ctsn 0: gpio                                                                                                                                                                                                                                                                                 |

| 1:0         | RW       | 0x0         | gpio0d0_sel GPIO0D[0] iomux select 01: uart2_rtsn 10: pmic_sleep 00: gpio                                                                                                                                                                                                                                                                |

### **GRF\_GPIO1A\_IOMUX**

Address: Operational Base + offset (0x00b8)

GPIO1A iomux control

| Bit   | Attr | Reset Value | Description                                |

|-------|------|-------------|--------------------------------------------|

|       |      |             | write enable                               |

|       |      |             | bit0~15 write enable                       |

|       |      |             | When bit 16=1, bit 0 can be written by     |

|       |      |             | software .                                 |

|       |      |             | When bit 16=0, bit 0 cannot be written by  |

|       |      |             | software;                                  |

|       |      |             | When bit 17=1, bit 1 can be written by     |

| 31:16 | WO   | 0x0000      | software .                                 |

|       |      |             | When bit 17=0, bit 1 cannot be written by  |

|       |      |             | software;                                  |

|       |      |             |                                            |

|       |      |             | When bit 31=1, bit 15 can be written by    |

|       |      |             | software .                                 |

|       |      |             | When bit 31=0, bit 15 cannot be written by |

|       |      |             | software;                                  |

| 15    | RO   | 0x0         | reserved                                   |

|       |      |             | gpio1a7_sel                                |

| 14    | RW   | 0x0         | GPIO1A[7] iomux select                     |

| -     |      | UXU         | 1: mmc0_wrprt                              |

|       |      |             | 0: gpio                                    |

| 13:12 | RO   | 0x0         | reserved                                   |

|       |      |             | gpio1a5_sel                                |

|       |      |             | GPIO1A[5] iomux select                     |

| 11:10 | RW   | 0x3         | 01: i2s_sdi                                |

|       |      |             | 10: sdmmc_data3                            |

|       |      |             | 00: gpio                                   |

|       |      |             | gpio1a4_sel                                |

|       |      |             | GPIO1A[4] iomux select                     |

| 9:8   | RW   | 0x0         | 01: i2s_sdo                                |

|       |      | *A^         | 10: sdmmc_data2                            |

| _     | D 0  | 0.0         | 00: gpio                                   |

| 7     | RO   | 0x0         | reserved                                   |

|       |      |             | gpio1a3_sel                                |

| 6     | RW 🔺 | 0x0         | GPIO1A[3] iomux select                     |

|       |      | <b>-</b>    | 1: i2s_lrcktx                              |

|       |      |             | 0: gpio                                    |

|       |      | /           | gpio1a2_sel                                |

| E. 4  | RW   | 0.0         | GPIO1A[2] iomux select                     |

| 5:4   | RVV  | 0x0         | 01: i2s_lrckrx                             |

|       |      |             | 10: sdmmc_data1<br>00: gpio                |

|       |      |             | i                                          |

|       |      |             | gpio1a1_sel<br>GPIO1A[1] iomux select      |

|       |      |             | O1: i2s_sclk                               |

| 3:2   | RW   | 0x0         | 10: sdmmc_data0                            |

|       |      |             | 11: pmic_sleep                             |

|       |      |             | 11: princ_sleep<br>  00: gpio              |

|       | I    |             | լսս. ցրա                                   |

# Rockchip RK3128 Technical Reference Manual Rev 1.0

| Bit | Attr | Reset Value | Description                                                                          |

|-----|------|-------------|--------------------------------------------------------------------------------------|

| 1:0 | RW   | 0x0         | gpio1a0_sel GPIO1A[0] iomux select 01: i2s_mclk 10: sdmmc_clkout 11: xin32k 00: gpio |

# GRF\_GPIO1B\_IOMUX

Address: Operational Base + offset (0x00bc)

GPIO1B iomux control

| Bit   | iomux c | Reset Value | Description                                                                                                                                                                                                                                                                                                                                        |

|-------|---------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIL   | Atti    | Reset value |                                                                                                                                                                                                                                                                                                                                                    |

| 31:16 | WO      | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software. When bit 31=0, bit 15 cannot be written by software; |

| 15    | RO      | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                           |

| 14    | RW      | 0×0         | gpio1b7_sel GPIO1B[7] iomux select 1: mmc0_cmd 0: gpio                                                                                                                                                                                                                                                                                             |

| 13    | RO      | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                           |

| 12    | RW      | 0×0         | gpio1b6_sel GPIO1B[6] iomux select 1: mmc0_pwren 0: gpio                                                                                                                                                                                                                                                                                           |

| 11:9  | RO      | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                           |

| 8     | RW      | 0x0         | <pre>gpio1b4_sel GPIO1B[4] iomux select 1: spi_csn1 0: gpio</pre>                                                                                                                                                                                                                                                                                  |

| 7:6   | RW      | 0x0         | gpio1b3_sel GPIO1B[3] iomux select 01: spi_csn0 10: uart1_rtsn 00: gpio                                                                                                                                                                                                                                                                            |

| 5:4   | RW      | 0x3         | <pre>gpio1b2_sel GPIO1B[2] iomux select 01: spi_rxd 10: uart1_sin 00: gpio</pre>                                                                                                                                                                                                                                                                   |

| Bit | Attr | Reset Value | Description                                                                       |

|-----|------|-------------|-----------------------------------------------------------------------------------|

| 3:2 | RW   | 0x0         | gpio1b1_sel GPIO1B[1] iomux select 01: spi_txd 10: uart1_sout 00: gpio            |

| 1:0 | RW   | 0x0         | <pre>gpio1b0_sel GPIO1B[0] iomux select 01: spi_clk 10: uart1_ctsn 00: gpio</pre> |

# GRF\_GPIO1C\_IOMUX

Address: Operational Base + offset (0x00c0)

GPIO1C iomux control

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                        |

|-------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | wo   | 0x0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software. When bit 31=0, bit 15 cannot be written by software; |

| 15:14 | RW   | 0x0         | gpio1c7_sel GPIO1C[7] iomux select 01: nand_cs3 10:emmc_rstnout 00: gpio                                                                                                                                                                                                                                                                           |

| 13:12 | RW   | 0x0         | <pre>gpio1c6_sel GPIO1C[6] iomux select 01: nand_cs2 10: emmc_cmd 00: gpio</pre>                                                                                                                                                                                                                                                                   |

| 11:10 | RW   | 0x0         | gpio1c5_sel GPIO1C[5] iomux select 10: jtag_tms when sdmmc0_detectn is invalid 01: mmc0_d3 00: gpio                                                                                                                                                                                                                                                |

| 9:8   | RW   | 0x0         | gpio1c4_sel GPIO1C[4] iomux select 10: jtag_tck when sdmmc0_detectn is invalid 01: mmc0_d2 00: gpio                                                                                                                                                                                                                                                |

| Bit | Attr | Reset Value | Description                                                          |

|-----|------|-------------|----------------------------------------------------------------------|

| 7:6 | RW   | 0×0         | gpio1c3_sel GPIO1C[3] iomux select 01: mmc0_d1 10: uart2_rx 00: gpio |

| 5:4 | RW   | 0×0         | gpio0c2_sel GPIO0C[2] iomux select 01:mmc0_d0 10: uart2_tx 00:gpio   |

| 3   | RO   | 0x0         | reserved                                                             |

| 2   | RW   | 0×0         | gpio1c1_sel GPIO1C[1] iomux select 1: mmc0_detn 0: gpio              |

| 1   | RO   | 0x0         | reserved                                                             |

| 0   | RW   | 0×0         | gpio1c0_sel GPIO1C[0] iomux select 1: mmc0_clkout 0: gpio            |

### **GRF\_GPIO1D\_IOMUX**

Address: Operational Base + offset (0x00c4)

GPIO1D iomux control

| Bit      | Attr | Reset Value | Description                                          |

|----------|------|-------------|------------------------------------------------------|

|          |      |             | write_enable                                         |

|          |      |             | bit0~15 write enable                                 |

|          |      |             | When bit 16=1, bit 0 can be written by               |

|          |      | * ^ ^       | software .                                           |

|          |      | 40          | When bit 16=0, bit 0 cannot be written by            |

|          |      |             | software;                                            |

|          |      |             | When bit 17=1, bit 1 can be written by               |

| 31:16    | WO   | 0x0000      | software.                                            |

|          |      |             | When bit 17=0, bit 1 cannot be written by            |

|          |      |             | software;                                            |

|          |      |             | Miles his 24 4 his 45 can be switten by              |

|          |      |             | When bit 31=1, bit 15 can be written by              |

| ( )      |      |             | software .                                           |

|          |      |             | When bit 31=0, bit 15 cannot be written by software; |

| <b>*</b> |      |             | gpio1d7_sel                                          |

|          |      |             | GPIO1D[7] iomux select                               |

| l        |      |             | 01: nand_d7                                          |

| 15:14    | RW   | 0x0         | 10: emmc_d7                                          |

|          |      |             | 11: spi_csn1                                         |

|          |      |             | 00: gpio                                             |

| Bit   | Attr     | Reset Value | Description                            |

|-------|----------|-------------|----------------------------------------|

|       |          |             | gpio1d6_sel GPIO1D[6] iomux select     |

| 13:12 | RW       | 0x0         | 01: nand_d6<br>10: emmc_d6             |

|       |          |             | 11: spi_csn0                           |

|       |          |             | 00: gpio                               |

|       |          |             | gpio1d5_sel                            |

|       |          |             | GPIO1D[5] iomux select                 |

| 11:10 | RW       | 0x0         | 01: nand_d5<br>10: emmc d5             |

|       |          |             | 11: spi_txd1                           |

|       |          |             | 00: gpio                               |

|       |          |             | gpio1d4_sel                            |

|       |          |             | GPIO1D[4] iomux select                 |

| 9:8   | RW       | 0x0         | 01: nand_d4                            |

| 3.0   | I VV     | 0.00        | 10: emmc_d4                            |

|       |          |             | 11: spi_rxd1                           |

|       |          |             | 00: gpio                               |

|       |          |             | gpio1d3_sel                            |

|       |          |             | GPIO1D[3] iomux select 01:nand_d3      |

| 7:6   | RW       | 0x0         | 10: emmc_d3                            |

|       |          |             | 11: sfc_d3                             |

|       |          |             | 00: gpio                               |

|       |          |             | gpio1d2_sel                            |

|       | RW       |             | GPIO1D[2] iomux select                 |

| 5:4   |          | 0x0         | 01: nand_d2                            |

| J. 1  |          |             | 10 : emmc_d2                           |

|       |          |             | 11: sfc_d2                             |

|       |          |             | 00: gpio<br>gpio1d1_sel                |

|       |          | 407         | GPIO101_sel<br> GPIO1D[1] iomux select |

|       |          |             | 01: nand d1                            |

| 3:2   | RW       | 0x0         | 10: emmc_d1                            |

|       | <b>A</b> | 1           | 11: sfc d1                             |

|       |          |             | 00: gpio                               |

|       |          | )           | gpio1d0_sel                            |

|       |          |             | GPIO1D[0] iomux select                 |

| 1:0   | RW       | 0×0         | 01: nand_d0                            |

|       |          |             | 10: emmc_d0                            |

|       |          |             | 11: sfc_d0                             |

|       | 1        |             | 00: gpio                               |

# GRF\_GPIO2A\_IOMUX

Address: Operational Base + offset (0x00c8)

GPIO2A iomux control

| Bit Attr Reset Value Description |

|----------------------------------|

|----------------------------------|

| Bit   | Attr | Reset Value | Description                                |

|-------|------|-------------|--------------------------------------------|

|       |      |             | write_enable                               |

|       |      |             | bit0~15 write enable                       |

|       |      |             | When bit 16=1, bit 0 can be written by     |

|       |      |             | software .                                 |

|       |      |             | When bit 16=0, bit 0 cannot be written by  |

|       |      |             | software;                                  |

|       |      |             | When bit 17=1, bit 1 can be written by     |

| 31:16 | WO   | 0x0000      | software .                                 |

|       |      |             | When bit 17=0, bit 1 cannot be written by  |

|       |      |             | software;                                  |

|       |      |             |                                            |

|       |      |             | When bit 31=1, bit 15 can be written by    |

|       |      |             | software .                                 |

|       |      |             | When bit 31=0, bit 15 cannot be written by |

|       |      |             | software;                                  |

|       |      |             | gpio2a7_sel<br>GPIO2A[7] iomux select      |

| 15:14 | RW   | 0x0         | 01: nand_dqs                               |

| 13.17 | IXVV | 0.00        | 10: emmc_clkout                            |

|       |      |             | 00: gpio                                   |

| 13    | RO   | 0x0         | reserved                                   |

|       | 1.10 |             | gpio2a6_sel                                |

| 4.0   | D)4/ |             | GPIO2A[6] iomux select                     |

| 12    | RW   | 0x0         | 1: nand_cs0                                |

|       |      |             | 0: gpio                                    |

|       |      |             | gpio2a5_sel                                |

|       |      |             | GPIO2A[5] iomux select                     |

| 11:10 | RW   | 0x0         | 01: nand_wp                                |

|       |      |             | 10: emmc_pwren                             |

|       |      | • 1         | 00: gpio                                   |

|       |      |             | gpio2a4_sel                                |

|       |      |             | GPIO2A[4] iomux select                     |

| 9:8   | RW   | 0x0         | 01: nand_rdy                               |

|       | A    | 1           | 10: emmc_cmd                               |

|       |      | <b>\</b>    | 11: sfc_clk<br>00: gpio                    |

|       |      |             | gpio2a3_sel                                |

|       |      | /           | GPIO2A[3] iomux select                     |

| 7:6   | RW   | 0x0         | 01: nand_rdn                               |

| スノ    |      |             | 10: sfc_csn1                               |

|       |      |             | 00: gpio                                   |

| 7     |      |             | gpio2a2_sel                                |

|       |      |             | GPIO2A[2] iomux select                     |

| 5:4   | RW   | 0x0         | 01:nand_wrn                                |

|       |      |             | 10: sfc_csn0                               |

|       |      |             | 00: gpio                                   |

|       |      |             | gpio2a1_sel                                |

| 3:2   | RW   | 0x0         | GPIO2A[1] iomux select                     |

|       |      |             | 01:nand_cle                                |

|       |      |             | 00: gpio                                   |

| Bit | Attr | Reset Value | Description                                                          |

|-----|------|-------------|----------------------------------------------------------------------|

| 1:0 | RW   |             | gpio2a0_sel GPIO2A[0] iomux select 01: nand_ale 10: spi_clk 00: gpio |

# GRF\_GPIO2B\_IOMUX

Address: Operational Base + offset (0x00cc)

GPIO2B iomux control

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                        |

|-------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | wo   | 0x0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software. When bit 31=0, bit 15 cannot be written by software; |

| 15:14 | RW   | 0x0         | gpio2b7_sel GPIO2B[7] iomux select 01: lcdc0_d13 10: ebc_sdce5 11: gmac_rxer 00: gpio                                                                                                                                                                                                                                                              |

| 13:12 | RW   | 0×0         | gpio2b6_sel GPIO2B[6] iomux select 01: lcdc0_d12 10: ebc_sdce4 11: gmac_clk 00: gpio                                                                                                                                                                                                                                                               |

| 11:10 | RW   | 0x0         | gpio2b5_sel GPIO2B[5] iomux select 01:lcdc0_d11 10: ebc_sdce3 11: gmac_txen 00: gpio                                                                                                                                                                                                                                                               |

| 9:8   | RW   | 0×0         | gpio2b4_sel GPIO2B[4] iomux select 01: lcdc0_d10 10: ebc_sdce2 11: gmac_mdio 00: gpio                                                                                                                                                                                                                                                              |

| Bit | Attr | Reset Value | Description                                                                             |

|-----|------|-------------|-----------------------------------------------------------------------------------------|

| 7:6 | RW   | 0×0         | gpio2b3_sel GPIO2B[3] iomux select 01: lcdc0_den 10: ebc_gdclk 11: gmac_rxclk 00: gpio  |

| 5:4 | RW   | 0×0         | gpio2b2_sel GPIO2B[2] iomux select 01: lcdc0_vsync 10: ebc_sdoe 11: gmac_crs 00: gpio   |

| 3:2 | RW   | 0x0         | gpio2b1_sel GPIO2B[1] iomux select 01: lcdc0_hsync 10: ebc_sdle 11: gmac_txclk 00: gpio |

| 1:0 | RW   | 0×0         | gpio2b0_sel GPIO2B[0] iomux select 01: lcdc0_dclk 10: ebc_sdclk 11: gmac_rxdv 00: gpio  |

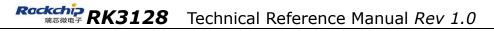

# GRF\_GPIO2C\_IOMUX

Address: Operational Base + offset (0x00d0)

GPIO2C iomux control

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                     |

|-------|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | wo   | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software. When bit 31=1, bit 15 can be written by software; |

| 15:8  | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                        |

| 7:6   | RW   | 0x0         | gpio2c3_sel GPIO2C[3] iomux select 01: lcdc0_d17 10: ebc_gdpwr0 11: gmac_txd0 00: gpio                                                                                                                                                                                                                                                          |

| Bit | Attr | Reset Value | Description                                                                          |

|-----|------|-------------|--------------------------------------------------------------------------------------|

| 5:4 | RW   | 0x0         | gpio2c2_sel GPIO2C[2] iomux select 01: lcdc0_d16 10: ebc_gdsp 11: gmac_txd1 00: gpio |

| 3:2 | RW   | 0×0         | gpio2c1_sel GPIO2C[1] iomux select 01: lcdc0_d15 10: ebc_gdoe 11: gmac_rxd0 00: gpio |

| 1:0 | RW   | 0x0         | gpio2c0_sel GPIO2C[0] iomux select 01:lcdc0_d14 10: ebc_vcom 11: gmac_rxd1 00: gpio  |

**GRF\_GPIO2D\_IOMUX**Address: Operational Base + offset (0x00d4)

GPIO2D iomux control

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                 |

|-------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | WO   | 0x0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; |

|       | C    |             | When bit 31=1, bit 15 can be written by software. When bit 31=0, bit 15 cannot be written by software;                                                                                                                                      |

| 15    | RO   | 0x0         | reserved                                                                                                                                                                                                                                    |

| 14:12 | RW   | 0x0         | gpio2d0_sel GPIO2D[0] iomux select 001: lcdc0_d22 010: ebc_gdpwr1 011: gps_clk 100: gmac_col 000: gpio                                                                                                                                      |

| 11:10 | RW   | 0x0         | gpio2d5_sel GPIO2D[5] iomux select 01: sc_det 10: uart0_ctsn 00: gpio                                                                                                                                                                       |

| Bit | Attr | Reset Value | Description                                                                           |

|-----|------|-------------|---------------------------------------------------------------------------------------|

| 9:8 | RO   | 0x0         | reserved                                                                              |

| 7:6 | RW   | 0×0         | gpio2d3_sel GPIO2D[3] iomux select 01: sc_clk 10: uart0_sin 00: gpio                  |

| 5:4 | RW   | 0x0         | gpio2d2_sel GPIO2D[2] iomux select 01: sc_rst 10: uart0_sout 00: gpio                 |

| 3:2 | RW   | 0×0         | gpio2d1_sel GPIO2D[1] iomux select 01: lcdc0_d23 10: ebc_gdpwr2 11: gmac_mdc 00: gpio |

| 1:0 | RO   | 0x0         | reserved                                                                              |

#### **GRF\_GPIO3A\_IOMUX**

Address: Operational Base + offset (0x00d8)

GPIO3A iomux control

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                        |

|-------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | wo   | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software. When bit 31=0, bit 15 cannot be written by software; |

| 15:0  | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                           |

### **GRF\_GPIO3B\_IOMUX**

Address: Operational Base + offset (0x00dc)

GPIO3B iomux control

| Bit Attr Reset Value | Description |

|----------------------|-------------|

|----------------------|-------------|

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                          |

|-------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | WO   | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software . When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software . When bit 31=0, bit 15 cannot be written by software; |

| 15:7  | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                             |

| 6     | RW   | 0x0         | gpio3a3_sel GPIO3A[3] iomux select 1: testclk_out 0: gpio                                                                                                                                                                                                                                                                                            |

| 5:0   | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                             |

# GRF\_GPIO3C\_IOMUX

Address: Operational Base + offset (0x00e0) GPIO3D iomux control

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                        |

|-------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | wo   | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software. When bit 31=0, bit 15 cannot be written by software; |

| 15:4  | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                           |

| 3:2   | RW   | 0×0         | gpio3c1_sel GPIO3C[1] iomux select 1: otg_drvvbus 0: gpio                                                                                                                                                                                                                                                                                          |

| 1:0   | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                           |

### **GRF\_GPIO3D\_IOMUX**

Address: Operational Base + offset (0x00e4)

#### GPIO3D iomux control

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                     |

|-------|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | WO   | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; When bit 31=1, bit 15 can be written by software. When bit 31=1, bit 15 can be written by software; |

| 15:7  | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                        |

| 6     | RW   | 0×0         | gpio3d3_sel GPIO3D[3] iomux select 1: spdif_tx 0: gpio                                                                                                                                                                                                                                                                                          |

| 5     | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                        |

| 4     | RW   | 0x0         | gpio3d2_sel GPIO3D[2] iomux select 1: pwm_irin 0: gpio                                                                                                                                                                                                                                                                                          |

| 3:0   | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                        |

# GRF\_GPIO2C\_IOMUX2

Address: Operational Base + offset (0x00e8)

GPIO2C iomux control

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                 |

|-------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | wo   | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; |

|       |      |             | When bit 31=1, bit 15 can be written by software. When bit 31=0, bit 15 cannot be written by software;                                                                                                                                      |

| 15    | RO   | 0x0         | reserved                                                                                                                                                                                                                                    |

#### GRF\_CIF\_IOMUX

Address: Operational Base + offset (0x00ec)

CIF iomux control

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                 |

|-------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | wo   | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; |

|       |      |             | When bit 31=1, bit 15 can be written by software. When bit 31=0, bit 15 cannot be written by software;                                                                                                                                      |

000: gpio

| Bit | Attr     | Reset Value | Description                     |

|-----|----------|-------------|---------------------------------|

| 15  | RO       | 0x0         | reserved                        |

|     |          |             | cifd7_sel                       |

| 1.4 | DW       | 0.40        | cif_d7 iomux select             |

| 14  | RW       | 0x0         | 1: ts_d7                        |

|     |          |             | 0: cif_d7                       |

| 13  | RO       | 0x0         | reserved                        |

|     |          |             | cifd6_sel                       |

| 12  | RW       | 0×0         | cif_d6 iomux select             |

| 12  | KVV      | 0.00        | 1: ts_d6                        |

|     |          |             | 0: cif_d6                       |

| 11  | RO       | 0x0         | reserved                        |

|     |          |             | cifd5_sel                       |

| 10  | RW       | 0x0         | cif_d5 iomux select             |

|     |          | 0.00        | 1: ts_d5                        |

|     |          |             | 0: cif_d5                       |

| 9   | RO       | 0x0         | reserved                        |

|     |          |             | cifd4_sel                       |

| 8   | RW       | 0x0         | cif_4 iomux select              |

|     |          |             | 1: ts_d4                        |

|     |          |             | 0: cif_d4                       |

| 7   | RO       | 0x0         | reserved                        |

|     |          |             | cifd3_sel                       |

| 6   | RW       | 0x0         | cif_d3 iomux select             |

|     |          |             | 1: ts_d3                        |

| Г   | DO.      | 0.40        | 0: cif_d3                       |

| 5   | RO       | 0x0         | reserved                        |

|     |          |             | cifd2_sel                       |

| 4   | RW       | 0x0         | cif_d2 iomux select<br>1: ts_d2 |

|     |          | • 4         | 0: cif_d2                       |

| 3   | RO       | 0x0         | reserved                        |

| 3   | KU       | UXU         | cifd1 sel                       |

|     |          |             | cif_d1 iomux select             |

| 2   | RW       | 0x0         | 1: ts_d1                        |

|     | <b>^</b> | 1           | 0: cif_d1                       |

| 1   | RO C     | 0×0         | reserved                        |

|     | INO .    |             | cifd0_sel                       |

|     |          |             | cif_d0 iomux select             |

| 0   | RW       | 0x0         | 1: ts_d0                        |

|     |          |             | 0: cif_d0                       |

|     |          | 1           | 10. 640                         |

# GRF\_CIF\_IOMUX1

Address: Operational Base + offset (0x00f0)

CIF iomux control register1

| Bit Attr Reset Value Description |

|----------------------------------|

|----------------------------------|

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                 |

|-------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | WO   | 0×0000      | write_enable bit0~15 write enable When bit 16=1, bit 0 can be written by software. When bit 16=0, bit 0 cannot be written by software; When bit 17=1, bit 1 can be written by software. When bit 17=0, bit 1 cannot be written by software; |