### **Chapter 44 GMAC Ethernet Interface**

### 44.1 Overview

The GMAC Ethernet Controller provides a complete Ethernet interface from processor to a Reduced Media Independent Interface (RMII) and Reduced Gigabit Media Independent Interface (RGMII) compliant Ethernet PHY.

The GMAC includes a DMA controller. The DMA controller efficiently moves packet data from microprocessor's RAM, formats the data for an IEEE 802.3-2002 compliant packet and transmits the data to an Ethernet Physical Interface (PHY). It also efficiently moves packet data from RXFIFO to microprocessor's RAM.

#### 44.1.1 Features

- Supports 10/100/1000-Mbps data transfer rates with the RGMII interfaces

- Supports 10/100-Mbps data transfer rates with the RMII interfaces

- Supports both full-duplex and half-duplex operation

- Supports CSMA/CD Protocol for half-duplex operation

- Supports packet bursting and frame extension in 1000 Mbps half-duplex operation

- Supports IEEE 802.3x flow control for full-duplex operation

- Optional forwarding of received pause control frames to the user application in full-duplex operation

- Back-pressure support for half-duplex operation

- Automatic transmission of zero-quanta pause frame on deassertion of flow control input in full-duplex operation

- Preamble and start-of-frame data (SFD) insertion in Transmit, and deletion in Receive paths

- Automatic CRC and pad generation controllable on a per-frame basis

- Options for Automatic Pad/CRC Stripping on receive frames

- Programmable frame length to support Standard Ethernet frames

- Programmable InterFrameGap (40-96 bit times in steps of 8)

- Supports a variety of flexible address filtering modes:

- 64-bit Hash filter (optional) for multicast and uni-cast (DA) addresses

- Option to pass all multicast addressed frames

- Promiscuous mode support to pass all frames without any filtering for network monitoring

- Passes all incoming packets (as per filter) with a status report

- Separate 32-bit status returned for transmission and reception packets

- Supports IEEE 802.1Q VLAN tag detection for reception frames

- MDIO Master interface for PHY device configuration and

management

- Support detection of LAN wake-up frames and AMD Magic Packet frames

- Support checksum off-load for received IPv4 and TCP packets encapsulated by the Ethernet frame

- Support checking IPv4 header checksum and TCP, UDP, or ICMP checksum encapsulated in IPv4 or IPv6 datagrams

- Comprehensive status reporting for normal operation and transfers with errors

- Support per-frame Transmit/Receive complete interrupt control

- Supports 4-KB receive FIFO depths on reception.

- Supports 2-KB FIFO depth on transmission

- Automatic generation of PAUSE frame control or backpressure signal to the GMAC core based on Receive FIFO-fill (threshold configurable) level

- Handles automatic retransmission of Collision frames for transmission

- Discards frames on late collision, excessive collisions, excessive deferral and underrun conditions

- AXI interface to any CPU or memory

- Software can select the type of AXI burst (fixed and variable length burst) in the AXI Master interface

- Supports internal loopback on the RGMII/RMII for debugging

- Debug status register that gives status of FSMs in Transmit and Receive data-paths and FIFO fill-levels.

### 44.2 Block Diagram

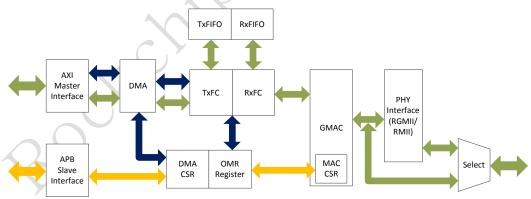

Fig. 44-1 GMAC architecture

The GMAC is broken up into multiple separate functional units. These blocks are interconnected in the MAC module. The block diagram shows the general flow of data and control signals between these blocks.

The GMAC transfers data to system memory through the AXI master interface. The host CPU uses the APB Slave interface to access the GMAC subsystem's control and status registers (CSRs).

The GMAC supports the PHY interfaces of reduced GMII (RGMII) and reduced MII (RMII).

The Transmit FIFO (Tx FIFO) buffers data read from system memory by the DMA before transmission by the GMAC Core. Similarly, the Receive FIFO (Rx FIFO) stores the Ethernet frames received from the line until they are transferred to system memory by the DMA. These are asynchronous FIFOs, as they also transfer the data between the application clock and the GMAC line clocks.

### **44.3 Function Description**

44.3.1 Frame Structure

Data frames transmitted shall have the frame format shown in Fig 32-2.

<inter-frame><preamble><sfd><data><efd>

#### Fig. 44-2 MAC Frame structure

The preamble <preamble> begins a frame transmission. The bit value of the preamble field consists of 7 octets with the following bit values:

10101010 10101010 10101010 10101010 10101010 10101010 10101010

The SFD (start frame delimiter) <sfd> indicates the start of a frame and follows the preamble. The bit value is 10101011.

The data in a well formed frame shall consist of N octets data.

44.3.2 RMII Interface timing diagram

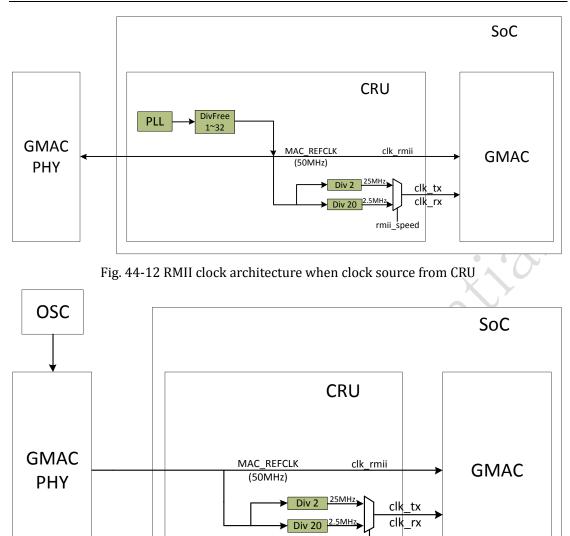

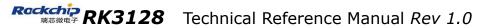

The Reduced Media Independent Interface (RMII) specification reduces the pin count between Ethernet PHYs and Switch ASICs (only in 10/100 mode). According to the IEEE 802.3u standard, an MII contains 16 pins for data and control. In devices incorporating multiple MAC or PHY interfaces (such as switches), the number of pins adds significant cost with increase in port count. The RMII specification addresses this problem by reducing the pin count to 7 for each port - a 62.5% decrease in pin count.

The RMII module is instantiated between the GMAC and the PHY. This helps translation of the MAC's MII into the RMII. The RMII block has the following characteristics:

• Supports 10-Mbps and 100-Mbps operating rates. It does not support 1000-Mbps operation.

• Two clock references are sourced externally or CRU, providing independent, 2-bit wide transmit and receive paths.

#### **Transmit Bit Ordering**

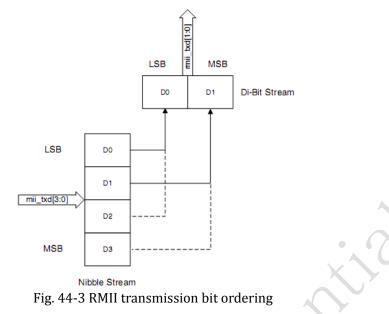

Each nibble from the MII must be transmitted on the RMII a di-bit at a time with the order of di-bit transmission shown in Fig.1-3. The lower order bits (D1 and D0) are transmitted first followed by higher order bits (D2 and D3).

#### **RMII Transmit Timing Diagrams**

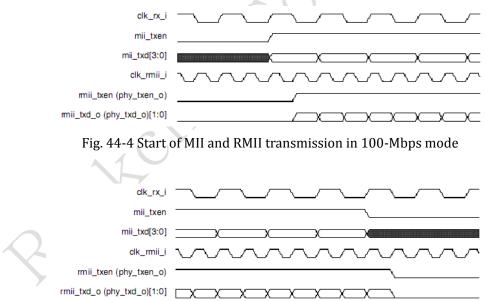

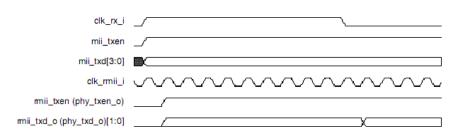

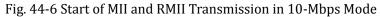

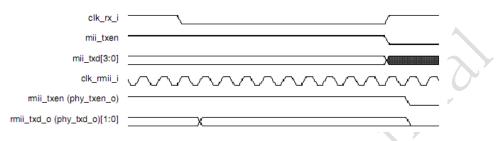

Fig.1-4 through 1-7 show MII-to-RMII transaction timing. The clk\_rmii\_i (REF\_CLK) frequency is 50MHz in RMII interface. In 10Mb/s mode, as the REF\_CLK frequency is 10 times as the data rate, the value on rmii\_txd\_o[1:0] (TXD[1:0]) shall be valid such that TXD[1:0] may be sampled every 10th cycle, regard-less of the starting cycle within the gRup and yield the correct frame data.

Fig. 44-5 End of MII and RMII Transmission in 100-Mbps Mode

#### **Receive Bit Ordering**

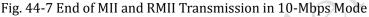

Each nibble is transmitted to the MII from the di-bit received from the RMII in the nibble transmission order shown in Fig.1-8. The lower order bits (D0 and D1) are received first, followed by the higher order bits (D2 and D3).

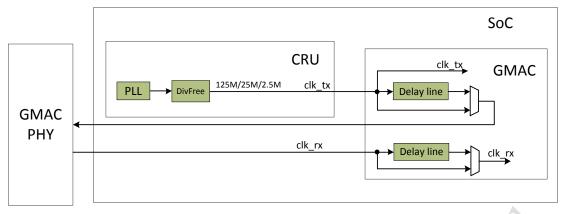

44.3.3 RGMII interface

The Reduced Gigabit Media Independent Interface (RGMII) specification reduces the pin count of the interconnection between the GMAC 10/100/1000 controller and the PHY for GMII and MII interfaces. To achieve this, the data path and control signals are reduced and multiplexed together with both the edges of the transmit and receive clocks. For gigabit operation the clocks operate at 125 MHz; for 10/100 operation, the clock rates are 2.5 MHz/25 MHz.

In the GMAC 10/100/1000 controller, the RGMII module is instantiated between

the GMAC core's GMII and the PHY to translate the control and data signals between the GMII and RGMII protocols.

The RGMII block has the following characteristics:

- Supports 10-Mbps, 100-Mbps, and 1000-Mbps operation rates.

- For the RGMII block, no extra clock is required because both the edges of the incoming clocks are used.

- The RGMII block extracts the in-band (link speed, duplex mode and link status) status signals from the PHY and provides them to the GMAC core logic for link detection.

#### 44.3.4 Management Interface

The MAC management interface provides a simple, two-wire, serial interface to connect the GMAC and a managed PHY, for the purposes of controlling the PHY and gathering status from the PHY. The management interface consists of a pair of signals that transport the management information across the MII bus: MDIO and MDC.

The GMAC initiates the management write/read operation. The clock gmii\_mdc\_o(MDC) is a divided clock from the application clock pclk\_gmac. The divide factor depends on the clock range setting in the GMII address register. Clock range is set as follows:

| Selection  | pclk_gmac   | MDC Clock     |

|------------|-------------|---------------|

| 0000       | 60-100 MHz  | pclk_gmac/42  |

| 0001       | 100-150 MHz | pclk_gmac/62  |

| 0010       | 20-35 MHz   | pclk_gmac/16  |

| 0011       | 35-60 MHz   | pclk_gmac/26  |

| 0100       | 150-250 MHz | pclk_gmac/102 |

| 0101       | 250-300 MHz | pclk_gmac/124 |

| 0110, 0111 | Reserved    |               |

The MDC is the derivative of the application clock pclk\_gmac. The management operation is performed through the gmii\_mdi\_i, gmii\_mdo\_o and gmii mdo o e signals. A three-state buffer is implemented in the PAD.

The frame structure on the MDIO line is shown below.

| IDLE PREAMBLE START OPCODE PHY ADDR ADDR TA DATA | IDLE | DLE |

|--------------------------------------------------|------|-----|

|--------------------------------------------------|------|-----|

Fig. 44-9 MDIO frame structure

|           | The mdio line is three-state; there is no clock on gmii_mdc_o<br>32 continuous bits of value 1<br>Start-of-frame is 2í01 |

|-----------|--------------------------------------------------------------------------------------------------------------------------|

| START:    |                                                                                                                          |

| OPCODE:   | 2'b10 for read and 2'b01 for write                                                                                       |

| PHY ADDR: | 5-bit address select for one of 32 PHYs                                                                                  |

| REG ADDR: | Register address in the selected PHY                                                                                     |

| TA:       | Turnaround is 2'bZ0 for read and 2'b10 for Write                                                                         |

| DATA:     | Any 16-bit value. In a write operation, the GMAC drives mdio; in a read operation, PHY drives it.                        |

#### 44.3.5 Power Management Block

Power management(PMT) supports the reception of network (remote) wake-up frames and Magic Packet frames. PMT does not perform the clock gate function, but generates interrupts for wake-up frames and Magic Packets received by the GMAC. The PMT block sits on the receiver path of the GMAC and is enabled with remote wake-up frame enable and Magic Packet enable. These enables are in the PMT control and status register and are programmed by the application.

When the power down mode is enabled in the PMT, then all received frames are dropped by the core and they are not forwarded to the application. The core comes out of the power down mode only when either a Magic Packet or a Remote Wake-up frame is received and the corresponding detection is enabled.

#### **Remote Wake-Up Frame Detection**

When the GMAC is in sleep mode and the remote wake-up bit is enabled in register GMAC\_PMT\_CTRL\_STA (0x002C), normal operation is resumed after receiving a remote wake-up frame. The application writes all eight wake-up filter registers, by performing a sequential write to address (0028). The application enables remote wake-up by writing a 1 to bit 2 of the register GMAC\_PMT\_CTRL\_STA.

PMT supports four programmable filters that allow support of different receive frame patterns. If the incoming frame passes the address filtering of Filter Command, and if Filter CRC-16 matches the incoming examined pattern, then the wake-up frame is received.

Filter\_offset (minimum value 12, which refers to the 13th byte of the frame) determines the offset from which the frame is to be examined. Filter Byte Mask determines which bytes of the frame must be examined. The thirty-first bit of Byte Mask must be set to zero.

The remote wake-up CRC block determines the CRC value that is compared with Filter CRC-16. The wake-up frame is checked only for length error, FCS error, dribble bit error, GMII error, collision, and to ensure that it is not a runt frame. Even if the wake-up frame is more than 512 bytes long, if the frame has a valid CRC value, it is considered valid. Wake-up frame detection is updated in the register GMAC\_PMT\_CTRL\_STA for every remote Wake-up frame received. A PMT interrupt to the application triggers a read to the GMAC\_PMT\_CTRL\_STA register to determine reception of a wake-up frame.

#### **Magic Packet Detection**

The Magic Packet frame is based on a method that uses Advanced Micro Device's Magic Packet technology to power up the sleeping device on the network. The GMAC receives a specific packet of information, called a Magic Packet, addressed to the node on the network.

Only Magic Packets that are addressed to the device or a broadcast address will be checked to determine whether they meet the wake-up requirements. Magic Packets that pass the address filtering (unicast or broadcast) will be checked to determine whether they meet the remote Wake-on-LAN data format of 6 bytes of all ones followed by a GMAC Address appearing 16 times.

The application enables Magic Packet wake-up by writing a 1 to Bit 1 of the register GMAC\_PMT\_CTRL\_STA. The PMT block constantly monitors each frame addressed to the node for a specific Magic Packet pattern. Each frame received is checked for a 48'hFF\_FF\_FF\_FF\_FF\_FF pattern following the destination and

source address field. The PMT block then checks the frame for 16 repetitions of the GMAC address without any breaks or interruptions. In case of a break in the 16 repetitions of the address, the 48'hFF\_FF\_FF\_FF\_FF\_FF pattern is scanned for again in the incoming frame. The 16 repetitions can be anywhere in the frame, but must be preceded by the synchronization stream

(48'hFF\_FF\_FF\_FF\_FF\_FF\_FF). The device will also accept a multicast frame, as long as the 16 duplications of the GMAC address are detected.

If the MAC address of a node is 48'h00\_11\_22\_33\_44\_55, then the GMAC scans for the data sequence:

Magic Packet detection is updated in the PMT Control and Status register for Magic Packet received. A PMT interrupt to the Application triggers a read to the PMT CSR to determine whether a Magic Packet frame has been received.

#### 44.3.6 MAC Management Counters

The counters in the MAC Management Counters (MMC) module can be viewed as an extension of the register address space of the CSR module. The MMC module maintains a set of registers for gathering statistics on the received and transmitted frames. These include a control register for controlling the behavior of the registers, two 32-bit registers containing interrupts generated (receive and transmit), and two 32-bit registers containing masks for the Interrupt register (receive and transmit). These registers are accessible from the Application through the MAC Control Interface (MCI). Non-32-bit accesses are allowed as long as the address is word-aligned.

The organization of these registers is shown in Register Description. The MMCs are accessed using transactions, in the same way the CSR address space is accessed. The Register Description in this chapter describe the various counters and list the address for each of the statistics counters. This address will be used for Read/Write accesses to the desired transmit/receive counter.

The MMC module gathers statistics on encapsulated IPv4, IPv6, TCP, UDP, or ICMP payloads in received Ethernet frames.

### 44.4 Register description

| Name                 | Offset | Size | Reset<br>Value | Description                |

|----------------------|--------|------|----------------|----------------------------|

| GMAC_MAC_CONF        | 0x0000 | W    | 0x0000000      | MAC Configuration Register |

| GMAC_MAC_FRM_FIL     | 0x0004 | W    | 0x00000000     | MAC Frame Filter           |

| GMAC_HASH_TAB_H<br>I | 0x0008 | W    | 0x0000000      | Hash Table High Register   |

| GMAC_HASH_TAB_L<br>O | 0x000c | W    | 0x0000000      | Hash Table Low Register    |

| GMAC_GMII_ADDR       | 0x0010 | W    | 0x0000000      | GMII Address Register      |

#### 44.4.1 Register Summary

|                | Name              | Offset | Size | Reset<br>Value | Description                                       |

|----------------|-------------------|--------|------|----------------|---------------------------------------------------|

| GMAC           | GMII_DATA         | 0x0014 | W    | 0x0000000      | GMII Data Register                                |

| GMAC_          | FLOW_CTRL         | 0x0018 | W    | 0x0000000      | Flow Control Register                             |

| GMAC_          | VLAN_TAG          | 0x001c | W    | 0x0000000      | VLAN Tag Register                                 |

| GMAC_          | DEBUG             | 0x0024 | W    | 0x00000000     | Debug register                                    |

| GMAC_<br>A     | _PMT_CTRL_ST      | 0x002c | w    | 0x0000000      | PMT Control and Status<br>Register                |

| GMAC_          | INT_STATUS        | 0x0038 | W    | 0x00000000     | Interrupt Status Register                         |

| GMAC_          | INT_MASK          | 0x003c | W    | 0x0000000      | Interrupt Mask Register                           |

| GMAC_<br>HI    | _MAC_ADDR0_       | 0x0040 | W    | 0x0000ffff     | MAC Address0 High Register                        |

| GMAC_<br>LO    | _MAC_ADDR0_       | 0x0044 | W    | 0xffffffff     | MAC Address0 Low Register                         |

| GMAC_          | AN_CTRL           | 0x00c0 | W    | 0x00000000     | AN Control Register                               |

| GMAC_          | AN_STATUS         | 0x00c4 | W    | 0x0000008      | AN Status Register                                |

| GMAC_          | _AN_ADV           | 0x00c8 | W    | 0x000001e0     | Auto_Negotiation<br>Advertisement Register        |

| GMAC_<br>T_AB  | AN_LINK_PAR       | 0x00cc | W    | 0x00000000     | Auto_Negotiation Link<br>Partner Ability Register |

| GMAC_          | _AN_EXP           | 0x00d0 | W    | 0x00000000     | Auto_Negotiation Expansion<br>Register            |

| GMAC_<br>STA   | INTF_MODE_        | 0x00d8 | W    | 0x0000000      | RGMII Status Register                             |

| GMAC_          | MMC_CTRL          | 0x0100 | W    | 0x0000000      | MMC Control Register                              |

| GMAC_<br>R     | _MMC_RX_INT       | 0x0104 | W    | 0x0000000      | MMC Receive Interrupt<br>Register                 |

| GMAC_<br>R     | _MMC_TX_INT       | 0x0108 | W    | 0x0000000      | MMC Transmit Interrupt<br>Register                |

| GMAC_<br>_MSK  | _MMC_RX_INT       | 0x010c | w    | 0x00000000     | MMC Receive Interrupt Mask<br>Register            |

| GMAC_<br>_MSK  | _MMC_TX_INT       | 0x0110 | w    | 0x00000000     | MMC Transmit Interrupt Mask<br>Register           |

| GMAC_<br>TCNT_ | _MMC_TXOCTE<br>GB | 0x0114 | W    | 0x00000000     | MMC TX OCTET Good and Bad<br>Counter              |

| GMAC_<br>NT_GB | _MMC_TXFRMC       | 0x0118 | w    | 0x00000000     | MMC TX Frame Good and Bad<br>Counter              |

| GMAC_<br>FLWER | _MMC_TXUND<br>R   | 0x0148 | W    | 0x00000000     | MMC TX Underflow Error                            |

| GMAC_<br>RR    | MMC_TXCARE        | 0x0160 | W    | 0x00000000     | MMC TX Carrier Error                              |

| GMAC_<br>TCNT_ | _MMC_TXOCTE<br>G  | 0x0164 | W    | 0x00000000     | MMC TX OCTET Good Counter                         |

| GMAC_<br>NT_G  | _MMC_TXFRMC       | 0x0168 | W    | 0x00000000     | MMC TX Frame Good Counter                         |

| GMAC_<br>CNT_G | _MMC_RXFRM<br>B   | 0x0180 | w    | 0x00000000     | MMC RX Frame Good and Bad<br>Counter              |

|                | MMC_RXOCTE        | 0x0184 | W    | 0x00000000     | MMC RX OCTET Good and Bad<br>Counter              |

|                | MMC_RXOCTE        | 0x0188 | W    | 0x00000000     | MMC RX OCTET Good Counter                         |

| Name                        | Offset | Size | Reset<br>Value | Description                                                |

|-----------------------------|--------|------|----------------|------------------------------------------------------------|

| GMAC_MMC_RXMCF              | 0.0100 | 14/  |                | MMC RX Mulitcast Frame                                     |

| RMCNT_G                     | 0x0190 | vv   | 0x0000000      | Good Counter                                               |

| GMAC_MMC_RXCRCE<br>RR       | 0x0194 | W    | 0x00000000     | MMC RX Carrier                                             |

| GMAC_MMC_RXLENE<br>RR       | 0x01c8 | W    | 0x0000000      | MMC RX Length Error                                        |

| GMAC_MMC_RXFIFO<br>OVRFLW   | 0x01d4 | W    | 0x00000000     | MMC RX FIFO Overflow                                       |

| GMAC_MMC_IPC_IN<br>T_MSK    | 0x0200 | w    | 0×00000000     | MMC Receive Checksum<br>Offload Interrupt Mask<br>Register |

| GMAC_MMC_IPC_IN<br>TR       | 0x0208 | W    | 0x00000000     | MMC Receive Checksum<br>Offload Interrupt Register         |

| GMAC_MMC_RXIPV4<br>GFRM     | 0x0210 | W    | 0x00000000     | MMC RX IPV4 Good Frame                                     |

| GMAC_MMC_RXIPV4<br>HDERRFRM | 0x0214 | W    | 0x00000000     | MMC RX IPV4 Head Error<br>Frame                            |

| GMAC_MMC_RXIPV6<br>GFRM     | 0x0224 | W    | 0×00000000     | MMC RX IPV6 Good Frame                                     |

| GMAC_MMC_RXIPV6<br>HDERRFRM | 0x0228 | W    | 0×00000000     | MMC RX IPV6 Head Error<br>Frame                            |

| GMAC_MMC_RXUDPE<br>RRFRM    | 0x0234 | W    | 0x0000000      | MMC RX UDP Error Frame                                     |

| GMAC_MMC_RXTCPE<br>RRFRM    | 0x023c | w    | 0×00000000     | MMC RX TCP Error Frame                                     |

| GMAC_MMC_RXICMP<br>ERRFRM   | 0x0244 | W    | 0×00000000     | MMC RX ICMP Error Frame                                    |

| GMAC_MMC_RXIPV4<br>HDERROCT | 0x0254 | w    | 0x00000000     | MMC RX OCTET IPV4 Head<br>Error                            |

| GMAC_MMC_RXIPV6<br>HDERROCT | 0x0268 | w    | 0x00000000     | MMC RX OCTET IPV6 Head<br>Error                            |

| GMAC_MMC_RXUDPE<br>RROCT    | 0x0274 | W    | 0×00000000     | MMC RX OCTET UDP Error                                     |

| GMAC_MMC_RXTCPE<br>RROCT    | 0x027c | W    | 0×00000000     | MMC RX OCTET TCP Error                                     |

| GMAC_MMC_RXICMP<br>ERROCT   | 0x0284 | W    | 0×00000000     | MMC RX OCTET ICMP Error                                    |

| GMAC_BUS_MODE               | 0x1000 | W    | 0x00020101     | Bus Mode Register                                          |

| GMAC_TX_POLL_DE<br>MAND     | 0x1004 | W    | 0x00000000     | Transmit Poll Demand<br>Register                           |

| GMAC_RX_POLL_DE<br>MAND     | 0x1008 | W    | 0×00000000     | Receive Poll Demand Register                               |

| GMAC_RX_DESC_LIS<br>T_ADDR  | 0x100c | W    | 0×00000000     | Receive Descriptor List<br>Address Register                |

| GMAC_TX_DESC_LIS<br>T_ADDR  | 0x1010 | W    | 0x0000000      | Transmit Descriptor List<br>Address Register               |

| GMAC_STATUS                 | 0x1014 | W    | 0x00000000     | Status Register                                            |

| GMAC_OP_MODE                | 0x1018 | W    | 0x00000000     | Operation Mode Register                                    |

| GMAC_INT_ENA                | 0x101c | W    | 0x0000000      | Interrupt Enable Register                                  |

| Name                          | Offset | Size | Reset<br>Value | Description                                                    |

|-------------------------------|--------|------|----------------|----------------------------------------------------------------|

| GMAC_OVERFLOW_C<br>NT         | 0x1020 | W    | 0x00000000     | Missed Frame and Buffer<br>Overflow Counter Register           |

| GMAC_REC_INT_WD<br>T_TIMER    | 0x1024 | W    | 0x0000000      | Receive Interrupt Watchdog<br>Timer Register                   |

| GMAC_AXI_BUS_MO<br>DE         | 0x1028 | W    | 0x00110001     | AXI Bus Mode Register                                          |

| GMAC_AXI_STATUS               | 0x102c | W    | 0x0000000      | AXI Status Register                                            |

| GMAC_CUR_HOST_T<br>X_DESC     | 0x1048 | w    | 0×00000000     | Current Host Transmit<br>Descriptor Register                   |

| GMAC_CUR_HOST_R<br>X_DESC     | 0x104c | W    | 0x0000000      | Current Host Receive<br>Descriptor Register                    |

| GMAC_CUR_HOST_T<br>X_Buf_ADDR | 0x1050 | W    | 0x00000000     | Current Host Transmit Buffer<br>Address Register               |

| GMAC_CUR_HOST_R<br>X_BUF_ADDR | 0x1054 | W    | 0x0000000      | Current Host Receive Buffer<br>Adderss Register                |

| GMAC_HW_FEA_REG               | 0x1058 | W    |                | The presence of the optional<br>features/functions of the core |

Notes: <u>Size</u> : **B** - Byte (8 bits) access, **HW** - Half WORD (16 bits) access, **W** -WORD (32 bits) access

### 44.4.2 Detail Register Description

#### GMAC\_MAC\_CONF

Address: Operational Base + offset (0x0000) MAC Configuration Register

| Bit   | Attr | <b>Reset Value</b> | Description                                                                                                                                                                                                                                                                                                                               |

|-------|------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:25 | RO   | 0x0                | reserved                                                                                                                                                                                                                                                                                                                                  |

| 24    | RW   | 0×0                | TC<br>Transmit Configuration in RGMII/SGMII/SMII<br>When set, this bit enables the transmission of<br>duplex mode, link speed, and link up/down<br>information to the PHY in the RGMII ports.<br>When this bit is reset, no such information is<br>driven to the PHY.                                                                     |

| 23    | RW   | 0×0                | WD<br>Watchdog Disable<br>When this bit is set, the GMAC disables the<br>watchdog timer on the receiver, and can<br>receive frames of up to 16,384 bytes.<br>When this bit is reset, the GMAC allows no<br>more than 2,048 bytes (10,240 if JE is set<br>high) of the frame being received and cuts off<br>any bytes received after that. |

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22    | RW   | 0×0         | JD<br>Jabber Disable<br>When this bit is set, the GMAC disables the<br>jabber timer on the transmitter, and can<br>transfer frames of up to 16,384 bytes.<br>When this bit is reset, the GMAC cuts off the<br>transmitter if the application sends out more<br>than 2,048 bytes of data (10,240 if JE is set<br>high) during transmission.                                                                                                        |

| 21    | RW   | 0×0         | BE<br>Frame Burst Enable<br>When this bit is set, the GMAC allows frame<br>bursting during transmission in GMII<br>Half-Duplex mode.                                                                                                                                                                                                                                                                                                              |

| 20    | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 19:17 | RW   | 0×0         | IFG<br>Inter-Frame Gap<br>These bits control the minimum IFG between<br>frames during transmission.<br>3'b000: 96 bit times<br>3'b001: 88 bit times<br>3'b010: 80 bit times<br><br>3'b111: 40 bit times                                                                                                                                                                                                                                           |

| 16    | RW   | 0×0         | DCRS<br>Disable Carrier Sense During Transmission<br>When set high, this bit makes the MAC<br>transmitter ignore the (G)MII CRS signal<br>during frame transmission in Half-Duplex<br>mode. This request results in no errors<br>generated due to Loss of Carrier or No Carrier<br>during such transmission. When this bit is low,<br>the MAC transmitter generates such errors<br>due to Carrier Sense and will even abort the<br>transmissions. |

| 15    | RW   | 0×0         | PS<br>Port Select<br>Selects between GMII and MII:<br>1'b0: GMII (1000 Mbps)<br>1'b1: MII (10/100 Mbps)                                                                                                                                                                                                                                                                                                                                           |

| 14    | RW   | 0×0         | FES<br>Speed<br>Indicates the speed in Fast Ethernet (MII)<br>mode:<br>1'b0: 10 Mbps<br>1'b1: 100 Mbps                                                                                                                                                                                                                                                                                                                                            |

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13  | RW   | 0×0         | DO<br>Disable Receive Own<br>When this bit is set, the GMAC disables the<br>reception of frames when the gmii_txen_o is<br>asserted in Half-Duplex mode.<br>When this bit is reset, the GMAC receives all<br>packets that are given by the PHY while<br>transmitting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12  | RW   | 0×0         | LM<br>Loopback Mode<br>When this bit is set, the GMAC operates in<br>loopback mode at GMII/MII. The (G)MII<br>Receive clock input (clk_rx_i) is required for<br>the loopback to work properly, as the<br>Transmit clock is not looped-back internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11  | RW   | 0×0         | DM<br>Duplex Mode<br>When this bit is set, the GMAC operates in a<br>Full-Duplex mode where it can transmit and<br>receive simultaneously. This bit is RO with<br>default value of 1'b1 in Full-Duplex-only<br>configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10  | RW   | 0×0         | IPC<br>Checksum Offload<br>When this bit is set, the GMAC calculates the<br>16-bit one's complement of the one's<br>complement sum of all received Ethernet<br>frame payloads. It also checks whether the<br>IPv4 Header checksum (assumed to be bytes<br>25-26 or 29-30 (VLAN-tagged) of the received<br>Ethernet frame) is correct for the received<br>frame and gives the status in the receive<br>status word. The GMAC core also appends the<br>16-bit checksum calculated for the IP header<br>datagram payload (bytes after the IPv4<br>header) and appends it to the Ethernet frame<br>transferred to the application (when Type 2<br>COE is deselected).<br>When this bit is reset, this function is disabled.<br>When Type 2 COE is selected, this bit, when<br>set, enables IPv4 checksum checking for<br>received frame payloads TCP/UDP/ICMP<br>headers. When this bit is reset, the COE<br>function in the receiver is disabled and the<br>corresponding PCE and IP HCE status bits are<br>always cleared. |

Rockchip RK3128 Technical Reference Manual Rev 1.0

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | RW   | 0x0         | DR<br>Disable Retry<br>When this bit is set, the GMAC will attempt<br>only 1 transmission. When a collision occurs<br>on the GMII/MII, the GMAC will ignore the<br>current frame transmission and report a<br>Frame Abort with excessive collision error in<br>the transmit frame status.<br>When this bit is reset, the GMAC will attempt<br>retries based on the settings of BL.                                                                                                                                                                                                                                  |

| 8   | RW   | 0x0         | LUD<br>Link Up/Down<br>Indicates whether the link is up or down<br>during the transmission of configuration in<br>RGMII interface:<br>1'b0: Link Down<br>1'b1: Link Up                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7   | RW   | 0x0         | ACS<br>Automatic Pad/CRC Stripping<br>When this bit is set, the GMAC strips the<br>Pad/FCS field on incoming frames only if the<br>length's field value is less than or equal to<br>1,500 bytes. All received frames with length<br>field greater than or equal to 1,501 bytes are<br>passed to the application without stripping the<br>Pad/FCS field.<br>When this bit is reset, the GMAC will pass all<br>incoming frames to the Host unmodified.                                                                                                                                                                |

| 6:5 | RW   | 0×0         | BL<br>Back-Off Limit<br>The Back-Off limit determines the random<br>integer number (r) of slot time delays (4,096<br>bit times for 1000 Mbps and 512 bit times for<br>10/100 Mbps) the GMAC waits before<br>rescheduling a transmission attempt during<br>retries after a collision. This bit is applicable<br>only to Half-Duplex mode and is reserved<br>(RO) in Full-Duplex-only configuration.<br>2'b00: k = min (n, 10)<br>2'b01: k = min (n, 8)<br>2'b10: k = min (n, 4)<br>2'b11: k = min (n, 1),<br>where n = retransmission attempt. The<br>random integer r takes the value in the range<br>$0 = r < 2^k$ |

Rockchip RK3128 Technical Reference Manual Rev 1.0

#### GMAC\_MAC\_FRM\_FILT

Address: Operational Base + offset (0x0004)

MAC Frame Filter

| Bit Attr Reset Value | Description |

|----------------------|-------------|

|----------------------|-------------|

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | RW   | 0x0         | RA<br>Receive All<br>When this bit is set, the GMAC Receiver<br>module passes to the Application all<br>frames received irrespective of whether they<br>pass the address filter. The result of the SA/DA<br>filtering is updated (pass or fail) in the<br>corresponding bits in the Receive Status<br>Word. When this bit is reset, the Receiver<br>module passes to the Application only those<br>frames that pass the SA/DA address filter.                                                                                          |

| 30:11 | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10    | RW   | 0x0         | HPF<br>Hash or Perfect Filter<br>When set, this bit configures the address filter<br>to pass a frame if it matches either the perfect<br>filtering or the hash filtering as set by HMC or<br>HUC bits. When low and if the HUC/HMC bit is<br>set, the frame is passed only if it matches the<br>Hash filter.                                                                                                                                                                                                                           |

| 9     | RW   | 0×0         | SAF<br>Source Address Filter Enable<br>The GMAC core compares the SA field of the<br>received frames with the values programmed<br>in the enabled SA registers. If the comparison<br>matches, then the SAMatch bit of RxStatus<br>Word is set high. When this bit is set high and<br>the SA filter fails, the GMAC drops the frame.<br>When this bit is reset, then the GMAC Core<br>forwards the received frame to the application<br>and with the updated SA Match bit of the<br>RxStatus depending on the SA address<br>comparison. |

| 8     | RW   | 0×0         | SAIF<br>SA Inverse Filtering<br>When this bit is set, the Address Check block<br>operates in inverse filtering mode for the SA<br>address comparison. The frames whose SA<br>matches the SA registers will be marked as<br>failing the SA Address filter.<br>When this bit is reset, frames whose SA does<br>not match the SA registers will be marked as<br>failing the SA Address filter.                                                                                                                                            |

Rockchip RK3128 Technical Reference Manual Rev 1.0

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:6 | RW   | 0×0         | PCF<br>Pass Control Frames<br>These bits control the forwarding of all control<br>frames (including unicast and multicast<br>PAUSE frames). Note that the processing of<br>PAUSE control frames depends only on RFE of<br>Register GMAC_FLOW_CTRL[2].<br>2'b00: GMAC filters all control frames from<br>reaching the application.<br>2'b01: GMAC forwards all control frames<br>except PAUSE control frames to application<br>even if they fail the Address filter.<br>2'b10: GMAC forwards all control frames to<br>application even if they fail the Address Filter.<br>2'b11: GMAC forwards control frames that<br>pass the Address Filter. |

| 5   | RW   | 0×0         | DBF<br>Disable Broadcast Frames<br>When this bit is set, the AFM module filters all<br>incoming broadcast frames.<br>When this bit is reset, the AFM module passes<br>all received broadcast frames.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4   | RW   | 0×0         | PM<br>Pass All Multicast<br>When set, this bit indicates that all received<br>frames with a multicast destination address<br>(first bit in the destination address field is '1')<br>are passed.<br>When reset, filtering of multicast frame<br>depends on HMC bit.                                                                                                                                                                                                                                                                                                                                                                             |

| 3   | RW   | 0×0         | DAIF<br>DA Inverse Filtering<br>When this bit is set, the Address Check block<br>operates in inverse filtering mode for the DA<br>address comparison for both unicast and<br>multicast frames.<br>When reset, normal filtering of frames is<br>performed.                                                                                                                                                                                                                                                                                                                                                                                      |

| 2   | RW   | 0×0         | HMC<br>Hash Multicast<br>When set, MAC performs destination address<br>filtering of received multicast frames<br>according to the hash table.<br>When reset, the MAC performs a perfect<br>destination address filtering for multicast<br>frames, that is, it compares the DA field with<br>the values programmed in DA registers.                                                                                                                                                                                                                                                                                                             |

| Bit | Attr | <b>Reset Value</b> | Description                                                                                                                                                                                                                                                                                                         |

|-----|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RW   | 0×0                | HUC<br>Hash Unicast<br>When set, MAC performs destination address<br>filtering of unicast frames according to the<br>hash table.<br>When reset, the MAC performs a perfect<br>destination address filtering for unicast<br>frames, that is, it compares the DA field with<br>the values programmed in DA registers. |

| 0   | RW   | 0×0                | PR<br>Promiscuous Mode<br>When this bit is set, the Address Filter module<br>passes all incoming frames regardless of its<br>destination or source address. The SA/DA<br>Filter Fails status bits of the Receive Status<br>Word will always be cleared when PR is set.                                              |

#### GMAC\_HASH\_TAB\_HI

Address: Operational Base + offset (0x0008) Hash Table High Register

| Bit  | Attr | <b>Reset Value</b> | Description                                                                      |

|------|------|--------------------|----------------------------------------------------------------------------------|

| 31:0 | RW   | 0x00000000         | HTH<br>Hash Table High<br>This field contains the upper 32 bits of Hash<br>table |

#### GMAC\_HASH\_TAB\_LO

Address: Operational Base + offset (0x000c)

Hash Table Low Register

| Bit  | Attr | <b>Reset Value</b> | Description                                                                     |

|------|------|--------------------|---------------------------------------------------------------------------------|

| 31:0 | RW   | $\alpha_{n}$       | HTL<br>Hash Table Low<br>This field contains the lower 32 bits of Hash<br>table |

#### GMAC\_GMII\_ADDR

Address: Operational Base + offset (0x0010) GMII Address Register

| Bit   | Attr | Reset Value | Description                                                                                                 |

|-------|------|-------------|-------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | 0x0         | reserved                                                                                                    |

| 15:11 | RW   | 0×00        | PA<br>Physical Layer Address<br>This field tells which of the 32 possible PHY<br>devices are being accessed |

| 10:6  | RW   | 0×00        | GR<br>GMII Register<br>These bits select the desired GMII register in<br>the selected PHY device            |

Rockchip RK3128 Technical Reference Manual Rev 1.0

|       |        | Reset Value | Description                                                         |

|-------|--------|-------------|---------------------------------------------------------------------|

|       |        |             | CR                                                                  |

|       |        |             | APB Clock Range                                                     |

|       |        |             | The APB Clock Range selection determines the                        |

|       |        |             | frequency of the MDC clock as per the                               |

|       |        |             | pclk_gmac frequency used in your design. The                        |

|       |        |             | suggested range of pclk_gmac frequency                              |

|       |        |             | applicable for each value below (when Bit[5]                        |

|       |        |             | = 0) ensures that the MDC clock is                                  |

|       |        |             | approximately between the frequency range                           |

|       |        |             | 1.0 MHz - 2.5 MHz.                                                  |

|       |        |             | Selection pclk_gmac MDC Clock                                       |

|       |        |             | 0000 60-100 MHz                                                     |

|       |        |             | pclk_gmac/42                                                        |

|       |        |             | 0001 100-150 MHz                                                    |

|       |        |             | pclk_gmac/62                                                        |

|       |        |             | 0010 20-35 MHz                                                      |

|       |        |             | pclk_gmac/16                                                        |

|       |        |             | 0011 35-60 MHz                                                      |

|       |        |             | pclk_gmac/26                                                        |

|       |        |             | 0100 150-250 MHz                                                    |

|       |        |             | pclk_gmac/102                                                       |

| 5:2 F | RW     | 0x0         | 0101 250-300 MHz                                                    |

|       |        |             | pclk_gmac/124                                                       |

|       |        |             | 0110, 0111 Reserved<br>When bit 5 is set, you can achieve MDC clock |

|       |        |             | of frequency higher than the IEEE                                   |

|       |        |             | 802.3 specified frequency limit of 2.5 MHz and                      |

|       |        |             | program a clock divider of lower                                    |

|       |        |             | value. For example, when pclk_gmac is of                            |

|       |        | •           | frequency 100 Mhz and you program these                             |

|       |        |             | bits as "1010", then the resultant MDC clock                        |

|       |        |             | will be of 12.5 Mhz which is outside the limit of                   |

|       |        | Y           | IEEE 802.3 specified range. Please program                          |

|       |        |             | the values given below only if the interfacing                      |

|       |        | 1           | chips supports faster MDC clocks.                                   |

|       |        |             | Selection MDC Clock                                                 |

|       |        |             | 1000 pclk_gmac/4                                                    |

|       | $\sim$ |             | 1001 pclk_gmac/6                                                    |

|       |        |             | 1010 pclk_gmac/8                                                    |

|       |        |             | 1011 pclk_gmac/10                                                   |

|       |        |             | 1100 pclk_gmac/12                                                   |

|       |        |             | 1101 pclk_gmac/14<br>1110 pclk_gmac/16                              |

|       |        |             | 1110 pcik_gmac/18                                                   |

| ++    |        |             | GW                                                                  |

|       |        |             | GMII Write                                                          |

|       |        |             | When set, this bit tells the PHY that this will be                  |

| 1 F   | RW     | 0x0         | a Write operation using register                                    |

| [     |        | -           | GMAC_GMII_DATA. If this bit is not set, this                        |

|       |        |             | will be a Read operation, placing the data in                       |

|       |        |             | register GMAC_GMII_DATA.                                            |

| Bit | Attr                                                          | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|---------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | W1C                                                           | 0×0         | GB<br>GMII Busy<br>This bit should read a logic 0 before writing to<br>Register GMII_ADDR and Register<br>GMII_DATA. This bit must also be set to 0<br>during a Write to Register GMII_ADDR. During<br>a PHY register access, this bit will be set to<br>1'b1 by the Application to indicate that a Read<br>or Write access is in progress. Register<br>GMII_DATA (GMII Data) should be kept valid<br>until this bit is cleared by the GMAC during a<br>PHY Write operation. The Register GMII_DATA<br>is invalid until this bit is cleared by the GMAC<br>during a PHY Read operation. The Register<br>GMII_ADDR (GMII Address) should not be<br>written to until this bit is cleared. |

|     | GMAC_GMII_DATA<br>Address: Operational Base + offset (0x0014) |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **GMAC\_GMII\_DATA**

Address: Operational Base + offset (0x0014)GMII Data Register

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                   |

|-------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RO   | 0x0         | reserved                                                                                                                                                                                                      |

| 15:0  | RW   | 0×0000      | GD<br>GMII Data<br>This contains the 16-bit data value read from<br>the PHY after a Management Read<br>operation or the 16-bit data value to be<br>written to the PHY before a Management Write<br>operation. |

#### GMAC\_FLOW\_CTRL

Address: Operational Base + offset (0x0018) Flow Control Register

| Bit   | Attr | <b>Reset Value</b> | Description                                                                                                                                                                                                                                                                                                                                                       |

|-------|------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:16 | RW   | 0x0000             | PT<br>Pause Time<br>This field holds the value to be used in the<br>Pause Time field in the transmit control frame.<br>If the Pause Time bits is configured to be<br>double-synchronized to the (G)MII clock<br>domain, then consecutive writes to this<br>register should be performed only after at<br>least 4 clock cycles in the destination clock<br>domain. |

| 15:8  | RO   | 0x0                | reserved                                                                                                                                                                                                                                                                                                                                                          |

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |      |             | DZPQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7   | RW   | 0×0         | Disable Zero-Quanta Pause<br>When set, this bit disables the automatic<br>generation of Zero-Quanta Pause Control<br>frames on the deassertion of the flow-control<br>signal from the FIFO layer (MTL or external<br>sideband flow control signal<br>sbd_flowctrl_i/mti_flowctrl_i).<br>When this bit is reset, normal operation with<br>automatic Zero-Quanta Pause Control frame<br>generation is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6   | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5:4 | RW   | 0×0         | PLT<br>Pause Low Threshold<br>This field configures the threshold of the<br>PAUSE timer at which the input flow control<br>signal mti_flowctrl_i (or sbd_flowctrl_i) is<br>checked for automatic retransmission of<br>PAUSE Frame. The threshold values should be<br>always less than the Pause Time configured in<br>Bits[31:16]. For example, if PT = 100H (256<br>slot-times), and PLT = 01, then a second<br>PAUSE frame is automatically transmitted if<br>the mti_flowctrl_i signal is asserted at 228<br>(256-28) slot-times after the first PAUSE<br>frame is transmitted.<br>Selection Threshold<br>00 Pause time minus 4 slot times<br>10 Pause time minus 28 slot times<br>11 Pause time minus 144 slot times<br>11 Pause time minus 256 slot times<br>Slot time is defined as time taken to transmit<br>512 bits (64 bytes) on the<br>GMII/MII interface. |

| 3   | RW   | 0×0         | UP<br>Unicast Pause Frame Detect<br>When this bit is set, the GMAC will detect the<br>Pause frames with the station's unicast<br>address specified in MAC Address0 High<br>Register and MAC Address0 Low Register, in<br>addition to the detecting Pause frames with<br>the unique multicast address. When this bit is<br>reset, the GMAC will detect only a Pause frame<br>with the unique multicast address specified in<br>the 802.3x standard.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2   | RW   | 0×0         | RFE<br>Receive Flow Control Enable<br>When this bit is set, the GMAC will decode the<br>received Pause frame and disable its<br>transmitter for a specified (Pause Time) time.<br>When this bit is reset, the decode function of<br>the Pause frame is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Rockchip RK3128 Technical Reference Manual Rev 1.0

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RW   | 0x0         | TFE<br>Transmit Flow Control Enable<br>In Full-Duplex mode, when this bit is set, the<br>GMAC enables the flow control operation to<br>transmit Pause frames. When this bit is reset,<br>the flow control operation in the GMAC is<br>disabled, and the GMAC will not transmit any<br>Pause frames.<br>In Half-Duplex mode, when this bit is set, the<br>GMAC enables the back-pressure operation.<br>When this bit is reset, the backpressure<br>feature is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 0   | RW   | 0×0         | FCB_BPA<br>Flow Control Busy/Backpressure Activate<br>This bit initiates a Pause Control frame in<br>Full-Duplex mode and activates the<br>backpressure function in Half-Duplex mode if<br>TFE bit is set.<br>In Full-Duplex mode, this bit should be read as<br>1'b0 before writing to the register<br>GMAC_FLOW_CTRL. To initiate a pause<br>control frame, the application must set this bit<br>to 1'b1. During a transfer of the control frame,<br>this bit will continue to be set to signify that a<br>frame transmission is in progress. After the<br>completion of Pause control frame<br>transmission, the GMAC will reset this bit to<br>1'b0. The register GMAC_FLOW_CTRL should<br>not be written to until this bit is cleared.<br>In Half-Duplex mode, when this bit is set (and<br>TFE is set), then backpressure is asserted by<br>the GMAC Core. During backpressure, when<br>the GMAC receives a new frame, the<br>transmitter starts sending a JAM pattern<br>resulting in a collision. This control register bit<br>is logically OR'ed with the mti_flowctrl_i input<br>signal for the backpressure function. |

**GMAC\_VLAN\_TAG** Address: Operational Base + offset (0x001c) VLAN Tag Register

| Bit   | Attr | <b>Reset Value</b> | Description |

|-------|------|--------------------|-------------|

| 31:17 | RO   | 0x0                | reserved    |

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|