## **Chapter 38 SAR-ADC**

#### 38.1 Overview

#### 38.1.1 Features

The ADC is a4-channel (0/1/2/6) signal-ended 10-bit Successive Approximation Register (SAR) A/D Converter. It uses the supply and ground as it reference which avoid use of any external reference. It converts the analog input signal into 10-bit binary digital codes at maximum conversion rate of 100KSPS with 1MHz A/D converter clock.

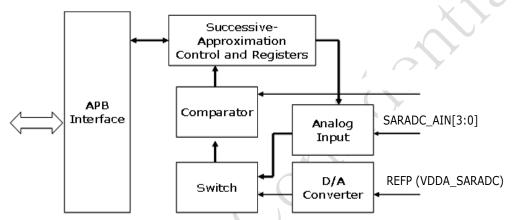

## 38.2 Block Diagram

Fig.38-1RKAudiSAR-ADC block diagram

## **Successive-Approximate Register and Control Logic Block**

This block is exploited to realize binary search algorithm, storing the intermediate result and generate control signal for analog block.

#### **Comparator Block**

This block compares the analog input SARADC\_AIN[3:0] with the voltage generated from D/A Converter, and output the comparison result to SAR and Control Logic Block for binary search. Three level amplifiers are employed in this comparator to provide enough gain.

# 38.3 Function description

In RKAudi, SAR-ADC works at single-sample operation mode.

This mode is useful to sample an analog input when there is a gap between two samples to be converted. In this mode START is asserted only on the rising edge of CLKIN where conversion is needed. At the end of every conversion EOC signal is made high and valid output data is available at the rising edge of EOC. The detailed timing diagram will be shown in the following.

## 38.4 Register Description

This section describes the control/status registers of the design.

## **38.4.1 Registers Summary**

| Name              | Offset |   | vallie     | Description                                           |

|-------------------|--------|---|------------|-------------------------------------------------------|

| SARADC_DATA       | 0x0000 | W | 0×00000000 | This register contains the data after A/D Conversion. |

| SARADC_STAS       | 0x0004 |   |            | The status register of A/D Converter.                 |

| SARADC_CTRL       | 0x0008 |   |            | The control register of A/D Converter.                |

| SARADC_DLY_PU_SOC | 0x000c | W | 0×00000000 | delay between power up<br>and start command           |

Notes: <u>Size</u>: **B**- Byte (8 bits) access, **HW**- Half WORD (16 bits) access, **W**-WORD (32 bits) access

# 38.4.2 Detail Register Description

#### SARADC\_DATA

Address: Operational Base + offset (0x0000)

This register contains the data after A/D Conversion.

| Bit   | Attr | Reset Value | Description                                            |

|-------|------|-------------|--------------------------------------------------------|

| 31:10 | RO   | 0x0         | reserved                                               |

| 9:0   | RO   | 0x000       | adc_data A/D value of the last conversion (DOUT[9:0]). |

## SARADC\_STAS

Address: Operational Base + offset (0x0004)

The status register of A/D Converter.

| Bit  | Attr | Reset Value | Description                                                             |

|------|------|-------------|-------------------------------------------------------------------------|

| 31:1 | RO 🛝 | 0x0         | reserved                                                                |

| 0    | RO   |             | adc_status ADC status (EOC) 1'b0: ADC stop 1'b1: Conversion in progress |

## SARADC\_CTRL

Address: Operational Base + offset (0x0008)

The control register of A/D Converter.

| Bit  | Attr     | <b>Reset Value</b> | Description                                     |  |  |

|------|----------|--------------------|-------------------------------------------------|--|--|

| 31:7 | RO       | 0x0                | reserved                                        |  |  |

|      |          |                    | int_status                                      |  |  |

| 6    | 6 RW 0x0 | 0.0                | Interrupt status.                               |  |  |

| U    |          | UXU                | This bit will be set to 1 when endofconversion. |  |  |

|      |          |                    | Set 0 to clear the interrupt.                   |  |  |

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                             |  |  |

|-----|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5   | RW   | 0×0         | int_en Interrupt enable. 1'b0: Disable 1'b1: Enable                                                                                                                                                                                     |  |  |

| 4   | RO   | 0x0         | reserved                                                                                                                                                                                                                                |  |  |

| 3   | RW   | 0×0         | adc_power_ctrl ADC power down control bit 1'b0: ADC power down 1'b1: ADC power up and reset start signal will be asserted (DLY_PU_SOC+2) sclk clock period later after power up                                                         |  |  |

| 2:0 | RW   | 0×0         | adc_input_src_sel ADC input source selection(CH_SEL[2:0]). 3'b000: Input source 0 (SARADC_AIN[0]) 3'b001: Input source 1 (SARADC_AIN[1]) 3'b010: Input source 2 (SARADC_AIN[2]) 3'b110: Input source 3 (SARADC_AIN[3]) Others: Reserved |  |  |

## SARADC\_DLY\_PU\_SOC

Address: Operational Base + offset (0x000c) delay between power up and start command

| Bit  | Attr | Reset Value | Description                                                                                                                                   |

|------|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 31:6 | RO   | 0x0         | reserved                                                                                                                                      |

| 5:0  | RW   | UXU8        | DLY_PU_SOC delay between power up and start command The start signal will be asserted (DLY_PU_SOC + 2) sclk clock period later after power up |

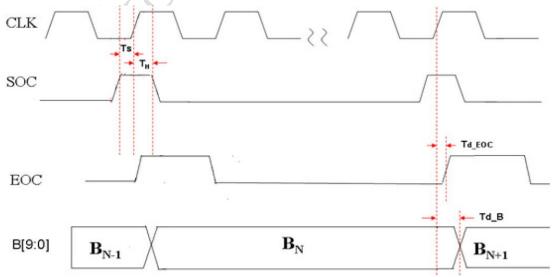

# 38.5 Timing Diagram

Fig.38-2SAR-ADC timing diagram in single-sample conversion mode

The following table has shows the detailed value for timing parameters in the

above diagram.

Table 38-1RKAudi SAR-ADC timing parameters list

| Timing     | Symbol           | Value |     | Unit | Description |                                  |

|------------|------------------|-------|-----|------|-------------|----------------------------------|

|            |                  | Min   | Тур | Max  |             |                                  |

| Data Setup | $T_{S}$          | 0     |     |      | ns          | Setup time for SOC               |

| Data Hold  | $T_{\mathrm{H}}$ | 10    |     |      | ns          | Hold time for SOC                |

| EOC delay  | $T_{D\_EOC}$     |       |     | 10.9 | ns          | EOC delay from rising edge of    |

|            |                  |       |     |      |             | CLK                              |

| Data delay | $T_{d\_B}$       |       |     | 11.1 | ns          | B[9:0] delay from rising edge of |

|            |                  |       |     |      |             | CLK                              |

| CLK        |                  | 90    |     |      | ns          | CLK period                       |

| period     |                  |       |     |      |             |                                  |

## 38.6 Application Notes

Steps of adc conversion:

- Write SARADC\_CTRL[3] as 0 to power down adc converter.

- Write SARADC\_CTRL[2:0] as n to select adc channel(n).

- Write SARADC\_CTRL[5] as 1 to enable adc interrupt.

- Write SARADC CTRL[3] as 1 to power up adc converter.

- Wait for adc interrupt or poll SARADC\_STAS register to assert whether the coversion is completed

- Read the conversion result from SARADC\_DATA[9:0]

Note: The A/D converter was designed to operate at maximum 1MHZ.