## **Chapter 36 Pulse Width Modulation(PWM)**

#### 36.1 Overview

The pulse-width modulator (PWM) feature is very common in embedded systems. It provides a way to generate a pulse periodic waveform for motor control or can act as a digital-to-analog converter with some external components.

#### **36.1.1 Features**

The PWMModule supports the following features:

- 4-built-in PWM channels

- Configurable to operate in capture mode

- Measures the high/low polarity effective cycles of this input waveform

- Generates a single interrupt at the transition of input waveform polarity

- 32-bit high polarity capture register

- 32-bit low polarity capture register

- 32-bit current value register

- Configurable to operate in continuous mode or one-shot mode

- 32-bit period counter

- 32-bit duty register

- 32-bit current value register

- Configurable PWM output polarity in inactive state and duty period pulse polarity

- Period and duty cycle are shadow buffered. Change takes effect when the end of the effective period is reached or when the channel is disabled

- Programmable center or left aligned outputs, and change takes effect when the end of the effective period is reached or when the channel is disabled

- 8-bit repeat counter for one-shot operation. One-shot operation will produce N + 1 periods of the waveform, where N is the repeat counter value, and generates a single interrupt at the end of operation

- Continuous mode generates the waveform continuously, and do not generates any interrupts

- pre-scaled operation to bus clock and then further scaled

- Available low-power mode to reduce power consumption when the channel is inactive.

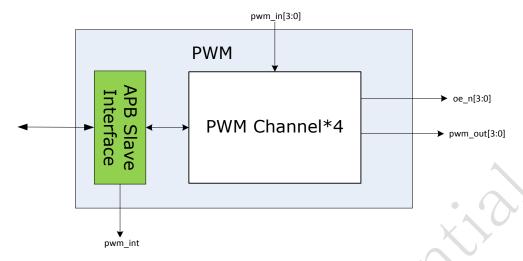

## 36.2 Block Diagram

Fig.36-1PWM architecture

#### 36.2.1 PWM APB Slave Interface

The host processor gets access to PWM Register Block through the APB slave interface with 32-bit bus width, and asserts the active-high level interrupt.

#### 36.2.2 PWM Channels

This is the control logic of PWM module, and controls the operation of PWM module according to the configured working mode.

## 36.3 Function description

The PWM supports three operation modes: reference mode, one-shot mode and continuous mode. For the one-shot mode and the continuous mode, the PWM output can be configured as the left-aligned mode or the center-aligned mode.

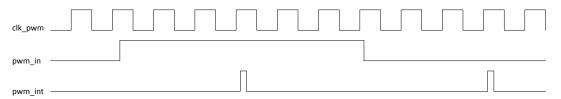

#### 36.3.1 Reference mode

The reference mode is used to measure the PWM channel input waveform high/low effective cycles with the PWM channel clock, and asserts an interrupt when the polarity of the input waveform changes. The number of the high effective cycles is recorded in the PWMx\_PERIOD\_HPC register, while the number of the low effective cycles is recorded in the PWMx\_DUTY\_LPC register.

Note: the PWM input waveform is doubled buffered when the PWM channel is working in order to filter unexpected shot-time polarity transition, and therefore the interrupt is asserted several cycles after the input waveform polarity changes, and so does the change of the values of PWMx\_PERIOD\_HPC and PWMx\_DUTY\_LPC.

Fig.36-2PWM Reference Mode

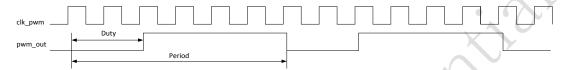

#### 36.3.2 Continuous Mode

The PWM channel generates a series of the pulsescontinuously asexpected once the channel is enabled with continuous mode.

In the continuous mode, the PWM output waveforms can be in one form of the two output mode: left-aligned mode or center-aligned mode.

For the left-aligned output mode, the PWM channel firstly starts the duty cycle with the configured duty polarity (PWMx\_CTRL.duty\_pol). Once duty cycle number (PWMx\_DUTY\_LPC) is reached, the output is switched to the opposite polarity. After the period number (PWMx\_PERIOD\_HPC) is reached, the output is again switched to the opposite polarity to start another period of desired pulse.

Fig.36-3PWM Left-aligned Output Mode

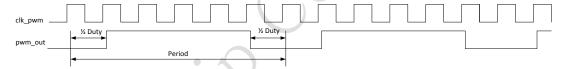

For the center-aligned output mode, the PWM channel firstly starts the duty cycle with the configured duty polarity (PWMx\_CTRL.duty\_pol). Once one half of duty cycle number (PWMx\_DUTY\_LPC) is reached, the output is switched to the opposite polarity. Then if there is one half of duty cycle left for the whole period , the output is again switched to the opposite polarity. Finally after the period number (PWMx\_PERIOD\_HPC) is reached, the output is again switched to the opposite polarity to start another period of desired pulse.

Fig.36-4PWM Center-aligned Output Mode

Disable the PWM channel, the channel stops generating the output waveforms and output polarity is fixed as the configured inactive polarity (PWMx\_CTRL.inactive\_pol).

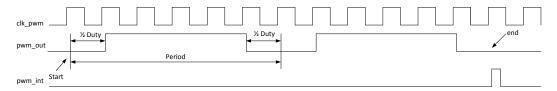

#### 36.3.3 One-shot Mode

Unlike the continuous mode, the PWM channel generates the output waveforms within the configured periods ( $PWM\_CTRL.rpt + 1$ ), and then stops. At the same times, an interrupt is asserted to inform that the operation has been finished.

There are also two output modes for the one-shot mode: the left-aligned mode and the center-aligned mode.

Fig.36-5PWM Center-aligned Output Mode

# 36.4 Register description

## 36.4.1 Register Summary

| Name                    | Offset | Size | Reset<br>Value | Description                                                        |

|-------------------------|--------|------|----------------|--------------------------------------------------------------------|

| PWM_PWM0_CNT            | 0x0000 | W    | 0x00000000     | PWM Channel 0 Counter<br>Register                                  |

| PWM_PWM0_PERIOD<br>_HPR | 0x0004 | W    | 0x00000000     | PWM Channel 0 Period<br>Register/High Polarity<br>Capture Register |

| PWM_PWM0_DUTY_L<br>PR   | 0x0008 | W    | 0x00000000     | PWM Channel 0 Duty<br>Register/Low Polarity Capture<br>Register    |

| PWM_PWM0_CTRL           | 0x000c | W    | 0×00000000     | PWM Channel 0 Control<br>Register                                  |

| PWM_PWM1_CNT            | 0x0010 | W    | 0×00000000     | PWM Channel 1 Counter<br>Register                                  |

| PWM_PWM1_PERIOD<br>_HPR | 0x0014 | w    | 0x00000000     | PWM Channel 1 Period<br>Register/High Polarity<br>Capture Register |

| PWM_PWM1_DUTY_L<br>PR   | 0x0018 | W    | 0x00000000     | PWM Channel 1 Duty<br>Register/Low Polarity Capture<br>Register    |

| PWM_PWM1_CTRL           | 0x001c | W    | 0×00000000     | PWM Channel 1 Control<br>Register                                  |

| PWM_PWM2_CNT            | 0x0020 | W    | 0x00000000     | PWM Channel 2 Counter<br>Register                                  |

| PWM_PWM2_PERIOD<br>_HPR | 0x0024 | W    | 0x00000000     | PWM Channel 2 Period<br>Register/High Polarity<br>Capture Register |

| PWM_PWM2_DUTY_L<br>PR   | 0x0028 | W    | 0x00000000     | PWM Channel 2 Duty<br>Register/Low Polarity Capture<br>Register    |

| PWM_PWM2_CTRL           | 0x002c | W    | 0×00000000     | PWM Channel 2 Control<br>Register                                  |

| PWM_PWM3_CNT            | 0x0030 | W    | 0x00000000     | PWM Channel 3 Counter<br>Register                                  |

| Name                    | Offset | Size | Reset<br>Value | Description                                                        |

|-------------------------|--------|------|----------------|--------------------------------------------------------------------|

| PWM_PWM3_PERIOD<br>_HPR | 0x0034 | W    | 0x00000000     | PWM Channel 3 Period<br>Register/High Polarity<br>Capture Register |

| PWM_PWM3_DUTY_L<br>PR   | 0x0038 | W    | 0x00000000     | PWM Channel 3 Duty<br>Register/Low Polarity Capture<br>Register    |

| PWM_PWM3_CTRL           | 0x003c | W    | 0×00000000     | PWM Channel 3 Control<br>Register                                  |

| PWM_INTSTS              | 0x0040 | W    | 0x00000000     | Interrupt Status Register                                          |

| PWM_INT_EN              | 0x0044 | W    | 0x00000000     | Interrupt Enable Register                                          |

Notes: Size: B- Byte (8 bits) access, HW- Half WORD (16 bits) access, W-WORD (32 bits) access

## **36.4.2 Detail Register Description**

### PWM\_PWM0\_CNT

Address: Operational Base + offset (0x0000)

PWM Channel 0 Counter Register

| Bit  | Attr | Reset Value | Description                                                                                                                                                    |

|------|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | RO   | 0×00000000  | CNT Timer Counter The 32-bit indicates current value of PWM Channel 0 counter. The counter runs at the rate of PWM clock. The value ranges from 0 to (2^32-1). |

### PWM\_PWM0\_PERIOD\_HPR

Address: Operational Base + offset (0x0004)

PWM Channel 0 Period Register/High Polarity Capture Register

| Bit | Attr | Reset Value | Description |

|-----|------|-------------|-------------|

|-----|------|-------------|-------------|

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                   |

|------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      |             | PERIOD_LPR                                                                                                                                                                                                                                                                                                    |

|      |      |             | Output Waveform Period/Input Waveform<br>High Polarity Cycle                                                                                                                                                                                                                                                  |

| 31:0 | RW   | 0×00000000  | If PWM is operated at the continuous mode or one-shot mode, this value defines the period of the output waveform. Note that, if the PWM is operated at the center-aligned mode, the period should be an even one, and therefore only the bit [31:1] is taken into account and bit [0] always considered as 0. |

|      |      |             | If PWM is operated at the capture mode, this value indicates the effective high polarity cycles of input waveform. This value is based on the PWM clock.                                                                                                                                                      |

|      |      |             | The value ranges from 0 to (2^32-1).                                                                                                                                                                                                                                                                          |

## PWM\_PWM0\_DUTY\_LPR

Address: Operational Base + offset (0x0008)

PWM Channel 0 Duty Register/Low Polarity Capture Register

| Bit  | Attr | Reset Value                                                                                                       | Description                                                                                                                                                                                                                                                                                                                    |

|------|------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      | • . <                                                                                                             | DUTY_LPR                                                                                                                                                                                                                                                                                                                       |

|      |      |                                                                                                                   | Output Waveform Duty Cycle/Input<br>Waveform Low Polarity Cycle                                                                                                                                                                                                                                                                |

| 31:0 | RW   | 0×00000000                                                                                                        | If PWM is operated at the continuous mode or one-shot mode, this value defines the duty cycle of the output waveform. The PWM starts the output waveform with duty cycle. Note that, if the PWM is operated at the center-aligned mode, the period should be an even one, and therefore only the [31:1] is taken into account. |

|      |      | If PWM is operated at the capture mode, this value indicates the effective low polarity cycles of input waveform. |                                                                                                                                                                                                                                                                                                                                |

|      |      |                                                                                                                   | This value is based on the PWM clock. The value ranges from 0 to (2^32-1).                                                                                                                                                                                                                                                     |

### PWM\_PWM0\_CTRL

Address: Operational Base + offset (0x000c)

## PWM Channel 0 Control Register

| Bit   | Attr | Reset Value | Description                                                                                                                                                                  |

|-------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |      |             | rpt                                                                                                                                                                          |

|       |      |             | Repeat Counter                                                                                                                                                               |

| 31:24 | RW   | 0×00        | This field defines the repeated effective periods of output waveform in one-shot mode. The value N means N+1 repeated effective periods.                                     |

|       |      |             | scale                                                                                                                                                                        |

|       |      |             | Scale Factor                                                                                                                                                                 |

| 23:16 | RW   | 0×00        | This fields defines the scale factor applied to prescaled clock. The value N means the clock is divided by 2*N. If N is 0, it means that the clock is divided by 512(2*256). |

| 15    | RO   | 0x0         | reserved                                                                                                                                                                     |

|       |      |             | prescale                                                                                                                                                                     |

|       |      |             | Prescale Factor                                                                                                                                                              |

| 14:12 | RW   | 0×0         | This field defines the prescale factor applied to input clock. The value N means that the input clock is divided by 2^N.                                                     |

| 11:10 | RO   | 0x0         | reserved                                                                                                                                                                     |

|       |      | •           | clk_sel                                                                                                                                                                      |

|       |      |             | Clock Source Select                                                                                                                                                          |

| 9     | RW   | 0×0         | 0: non-scaled clock is selected as PWM clock source. It means that the prescale clock is directly used as the PWM clock source                                               |

|       | C    |             | 1: scaled clock is selected as PWM clock source                                                                                                                              |

| 2     |      |             | lp_en                                                                                                                                                                        |

|       |      |             | Low Power Mode Enable                                                                                                                                                        |

|       |      |             | 0: disabled                                                                                                                                                                  |

| 8     | RW   | 0x0         | 1: enabled                                                                                                                                                                   |

|       |      |             | When PWM channel is inactive state and Low Power Mode is enabled, the path to PWM Clock prescale module is blocked to reduce power consumption.                              |

| 7:6   | RO   | 0x0         | reserved                                                                                                                                                                     |

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                  |

|-----|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5   | RW   | 0×0         | output_mode PWM Output mode 0: left aligned mode 1: center aligned mode                                                                                                                                                                                                                      |

| 4   | RW   | 0×0         | inactive_pol Inactive State Output Polarity This defines the output waveform polarity when PWM channel is in inactive state. The inactive state means that PWM finishes the complete waveform in one-shot mode or PWM channel is disabled.  0: negative 1: positive                          |

| 3   | RW   | 0×0         | duty_pol Duty Cycle Output Polarity This defines the polarity for duty cycle. PWM starts the output waveform with duty cycle. 0: negative 1: positive                                                                                                                                        |

| 2:1 | RW   | 0×0         | pwm_mode  PWM Operation Mode  00: One shot mode. PWM produces the waveform within the repeated times defined by PWMx_CTRL_rpt.  01: Continuous mode. PWM produces the waveform continuously  10: Capture mode. PWM measures the cycles of high/low polarity of input waveform.  11: reserved |

| 0   | RW   | 0×0         | pwm_en PWM channel enable 0: disabled 1: enabled. If the PWM is worked the one-shot mode, this bit will be cleared at the end of operation                                                                                                                                                   |

#### PWM\_PWM1\_CNT

Address: Operational Base + offset (0x0010)

PWM Channel 1 Counter Register

| Bit  | Attr | Reset Value | Description                                                                                             |

|------|------|-------------|---------------------------------------------------------------------------------------------------------|

|      |      |             | CNT                                                                                                     |

|      |      |             | Timer Counter                                                                                           |

| 31:0 | RO   | 0×00000000  | The 32-bit indicates current value of PWM Channel 1 counter. The counter runs at the rate of PWM clock. |

|      |      |             | The value ranges from 0 to $(2^32-1)$ .                                                                 |

#### PWM\_PWM1\_PERIOD\_HPR

Address: Operational Base + offset (0x0014)

PWM Channel 1 Period Register/High Polarity Capture Register

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                   |

|------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      |             | PERIOD_LPR                                                                                                                                                                                                                                                                                                    |

|      |      |             | Output Waveform Period/Input Waveform<br>High Polarity Cycle                                                                                                                                                                                                                                                  |

| 31:0 | RW   | 0×00000000  | If PWM is operated at the continuous mode or one-shot mode, this value defines the period of the output waveform. Note that, if the PWM is operated at the center-aligned mode, the period should be an even one, and therefore only the bit [31:1] is taken into account and bit [0] always considered as 0. |

| 2    | 0    |             | If PWM is operated at the capture mode, this value indicates the effective high polarity cycles of input waveform.                                                                                                                                                                                            |

|      |      |             | This value is based on the PWM clock. The value ranges from 0 to (2^32-1).                                                                                                                                                                                                                                    |

#### PWM\_PWM1\_DUTY\_LPR

Address: Operational Base + offset (0x0018)

PWM Channel 1 Duty Register/Low Polarity Capture Register

| Bit | Attr | Reset Value | Description |

|-----|------|-------------|-------------|

|-----|------|-------------|-------------|

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                    |

|------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      |             | DUTY_LPR                                                                                                                                                                                                                                                                                                                       |

|      |      |             | Output Waveform Duty Cycle/Input<br>Waveform Low Polarity Cycle                                                                                                                                                                                                                                                                |

| 31:0 | RW   |             | If PWM is operated at the continuous mode or one-shot mode, this value defines the duty cycle of the output waveform. The PWM starts the output waveform with duty cycle. Note that, if the PWM is operated at the center-aligned mode, the period should be an even one, and therefore only the [31:1] is taken into account. |

|      |      |             | If PWM is operated at the capture mode, this value indicates the effective low polarity cycles of input waveform.                                                                                                                                                                                                              |

|      |      |             | This value is based on the PWM clock. The value ranges from 0 to (2^32-1).                                                                                                                                                                                                                                                     |

## PWM\_PWM1\_CTRL

Address: Operational Base + offset (0x001c)

PWM Channel 1 Control Register

| Bit   | Attr | Reset Value | Description                                                                                                                                                                  |

|-------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |      |             | rpt                                                                                                                                                                          |

|       |      |             | Repeat Counter                                                                                                                                                               |

| 31:24 | RW   | 0×00        | This field defines the repeated effective periods of output waveform in one-shot mode. The value N means N+1 repeated effective periods.                                     |

|       |      |             | scale                                                                                                                                                                        |

| 1     |      |             | Scale Factor                                                                                                                                                                 |

| 23:16 | RW   | 0×00        | This fields defines the scale factor applied to prescaled clock. The value N means the clock is divided by 2*N. If N is 0, it means that the clock is divided by 512(2*256). |

| 15    | RO   | 0x0         | reserved                                                                                                                                                                     |

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                    |

|-------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |      |             | prescale                                                                                                                                                                                       |

|       |      |             | Prescale Factor                                                                                                                                                                                |

| 14:12 | RW   | 0×0         | This field defines the prescale factor applied to input clock. The value N means that the input clock is divided by 2^N.                                                                       |

| 11:10 | RO   | 0x0         | reserved                                                                                                                                                                                       |

|       |      |             | clk_sel                                                                                                                                                                                        |

|       |      |             | Clock Source Select                                                                                                                                                                            |

| 9     | RW   | 0×0         | 0: non-scaled clock is selected as PWM clock source. It means that the prescale clock is directly used as the PWM clock source                                                                 |

|       |      |             | 1: scaled clock is selected as PWM clock source                                                                                                                                                |

|       |      |             | lp_en                                                                                                                                                                                          |

|       |      |             | Low Power Mode Enable                                                                                                                                                                          |

|       |      | 0x0         | 0: disabled                                                                                                                                                                                    |

| 8     | RW   |             | 1: enabled                                                                                                                                                                                     |

|       |      |             | When PWM channel is inactive state and Low Power Mode is enabled, the path to PWM Clock prescale module is blocked to reduce power consumption.                                                |

| 7:6   | RO   | 0x0         | reserved                                                                                                                                                                                       |

|       | RW   | RW 0x0      | output_mode                                                                                                                                                                                    |

| 5     |      |             | PWM Output mode                                                                                                                                                                                |

|       |      | 0.0         | 0: left aligned mode                                                                                                                                                                           |

|       |      | /           | 1: center aligned mode                                                                                                                                                                         |

| 2     |      |             | inactive_pol                                                                                                                                                                                   |

|       |      |             | Inactive State Output Polarity                                                                                                                                                                 |

| 4     | RW   | 0×0         | This defines the output waveform polarity when PWM channel is in inactive state. The inactive state means that PWM finishes the complete waveform in one-shot mode or PWM channel is disabled. |

|       |      |             | 0: negative                                                                                                                                                                                    |

|       |      |             | 1: positive                                                                                                                                                                                    |

|       |      |             |                                                                                                                                                                                                |

| Bit | Attr | Reset Value | Description                                                                                          |

|-----|------|-------------|------------------------------------------------------------------------------------------------------|

|     |      |             | duty_pol                                                                                             |

|     |      |             | Duty Cycle Output Polarity                                                                           |

| 3   | RW   | 0x0         | This defines the polarity for duty cycle. PWM starts the output waveform with duty cycle.            |

|     |      |             | 0: negative                                                                                          |

|     |      |             | 1: positive                                                                                          |

|     |      |             | pwm_mode                                                                                             |

|     |      | 0x0         | PWM Operation Mode                                                                                   |

|     | RW   |             | 00: One shot mode. PWM produces the waveform within the repeated times defined by PWMx_CTRL_rpt      |

| 2:1 |      |             | 01: Continuous mode. PWM produces the waveform continuously                                          |

|     |      |             | 10: Capture mode. PWM measures the cycles of high/low polarity of input waveform.                    |

|     |      |             | 11: reserved                                                                                         |

|     |      | V 0×0       | pwm_en                                                                                               |

| 0   |      |             | PWM channel enable                                                                                   |

|     | RW   |             | 0: disabled                                                                                          |

|     |      |             | 1: enabled. If the PWM is worked the one-shot mode, this bit will be cleared at the end of operation |

## PWM\_PWM2\_CNT

Address: Operational Base + offset (0x0020)

PWM Channel 2 Counter Register

| Bit  | Attr | Reset Value | Description                                                                                             |

|------|------|-------------|---------------------------------------------------------------------------------------------------------|

|      |      |             | CNT<br>Timer Counter                                                                                    |

| 31:0 | RO   |             | The 32-bit indicates current value of PWM Channel 2 counter. The counter runs at the rate of PWM clock. |

|      |      |             | The value ranges from 0 to (2^32-1).                                                                    |

## PWM\_PWM2\_PERIOD\_HPR

Address: Operational Base + offset (0x0024)

PWM Channel 2 Period Register/High Polarity Capture Register

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                   |

|------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 |      | 0×00000000  | PERIOD_LPR                                                                                                                                                                                                                                                                                                    |

|      | RW   |             | Output Waveform Period/Input Waveform<br>High Polarity Cycle                                                                                                                                                                                                                                                  |

|      |      |             | If PWM is operated at the continuous mode or one-shot mode, this value defines the period of the output waveform. Note that, if the PWM is operated at the center-aligned mode, the period should be an even one, and therefore only the bit [31:1] is taken into account and bit [0] always considered as 0. |

|      |      |             | If PWM is operated at the capture mode, this value indicates the effective high polarity cycles of input waveform.                                                                                                                                                                                            |

|      |      |             | This value is based on the PWM clock. The value ranges from 0 to (2^32-1).                                                                                                                                                                                                                                    |

## PWM\_PWM2\_DUTY\_LPR

Address: Operational Base + offset (0x0028)

PWM Channel 2 Duty Register/Low Polarity Capture Register

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                    |

|------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      | 10'         | DUTY_LPR                                                                                                                                                                                                                                                                                                                       |

|      | RW   | 0×00000000  | Output Waveform Duty Cycle/Input<br>Waveform Low Polarity Cycle                                                                                                                                                                                                                                                                |

| 31:0 |      |             | If PWM is operated at the continuous mode or one-shot mode, this value defines the duty cycle of the output waveform. The PWM starts the output waveform with duty cycle. Note that, if the PWM is operated at the center-aligned mode, the period should be an even one, and therefore only the [31:1] is taken into account. |

|      |      |             | If PWM is operated at the capture mode, this value indicates the effective low polarity cycles of input waveform.                                                                                                                                                                                                              |

|      |      |             | This value is based on the PWM clock. The value ranges from 0 to (2^32-1).                                                                                                                                                                                                                                                     |

## PWM\_PWM2\_CTRL

Address: Operational Base + offset (0x002c)

PWM Channel 2 Control Register

| Bit   | Attr | Reset Value | Description                                                                                                                                                                  |

|-------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |      |             | rpt                                                                                                                                                                          |

|       |      |             | Repeat Counter                                                                                                                                                               |

| 31:24 | RW   | 0×00        | This field defines the repeated effective periods of output waveform in one-shot mode. The value N means N+1 repeated effective periods.                                     |

|       |      |             | scale                                                                                                                                                                        |

|       |      |             | Scale Factor                                                                                                                                                                 |

| 23:16 | RW   | 0×00        | This fields defines the scale factor applied to prescaled clock. The value N means the clock is divided by 2*N. If N is 0, it means that the clock is divided by 512(2*256). |

| 15    | RO   | 0x0         | reserved                                                                                                                                                                     |

|       |      |             | prescale                                                                                                                                                                     |

|       |      |             | Prescale Factor                                                                                                                                                              |

| 14:12 | RW   | 0x0         | This field defines the prescale factor applied to input clock. The value N means that the input clock is divided by 2^N.                                                     |

| 11:10 | RO   | 0x0         | reserved                                                                                                                                                                     |

|       | _    | 10          | clk_sel                                                                                                                                                                      |

|       |      |             | Clock Source Select                                                                                                                                                          |

| 9     | RW   | 0×0         | 0: non-scaled clock is selected as PWM clock source. It means that the prescale clock is directly used as the PWM clock source                                               |

|       |      |             | 1: scaled clock is selected as PWM clock source                                                                                                                              |

| Bit      | Attr | Reset Value | Description                                                                                                                                                                                    |

|----------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |             | lp_en                                                                                                                                                                                          |

|          |      |             | Low Power Mode Enable                                                                                                                                                                          |

|          |      |             | 0: disabled                                                                                                                                                                                    |

| 8        | RW   | 0x0         | 1: enabled                                                                                                                                                                                     |

|          |      |             | When PWM channel is inactive state and Low Power Mode is enabled, the path to PWM Clock prescale module is blocked to reduce power consumption.                                                |

| 7:6      | RO   | 0x0         | reserved                                                                                                                                                                                       |

|          |      |             | output_mode                                                                                                                                                                                    |

| _        | DW   | 0.40        | PWM Output mode                                                                                                                                                                                |

| 5        | RW   | 0x0         | 0: left aligned mode                                                                                                                                                                           |

|          |      |             | 1: center aligned mode                                                                                                                                                                         |

|          |      |             | inactive_pol                                                                                                                                                                                   |

|          |      |             | Inactive State Output Polarity                                                                                                                                                                 |

| 4        | RW   | 0×0         | This defines the output waveform polarity when PWM channel is in inactive state. The inactive state means that PWM finishes the complete waveform in one-shot mode or PWM channel is disabled. |

|          |      | • . <       | 0: negative                                                                                                                                                                                    |

|          |      |             | 1: positive                                                                                                                                                                                    |

|          | _    | 19          | duty_pol                                                                                                                                                                                       |

|          |      |             | Duty Cycle Output Polarity                                                                                                                                                                     |

| 3        | RW   | 0×0         | This defines the polarity for duty cycle. PWM starts the output waveform with duty cycle.                                                                                                      |

| 1        | _    |             | 0: negative                                                                                                                                                                                    |

| <b>Y</b> |      |             | 1: positive                                                                                                                                                                                    |

| Bit | Attr | Reset Value | Description                                                                                                                                                                                  |

|-----|------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2:1 | RW   | 0×0         | pwm_mode  PWM Operation Mode  00: One shot mode. PWM produces the waveform within the repeated times defined by PWMx_CTRL_rpt.                                                               |

|     |      |             | <ul><li>01: Continuous mode. PWM produces the waveform continuously</li><li>10: Capture mode. PWM measures the cycles of high/low polarity of input waveform.</li><li>11: reserved</li></ul> |

| 0   | RW   | 0x0         | pwm_en PWM channel enable 0: disabled 1: enabled. If the PWM is worked the one-shot mode, this bit will be cleared at the end of operation                                                   |

## PWM\_PWM3\_CNT

Address: Operational Base + offset (0x0030)

PWM Channel 3 Counter Register

| Bit  | Attr | Reset Value | Description                                                                                             |

|------|------|-------------|---------------------------------------------------------------------------------------------------------|

|      |      |             | CNT                                                                                                     |

|      |      | 1-          | Timer Counter                                                                                           |

| 31:0 | RO   | 0×00000000  | The 32-bit indicates current value of PWM Channel 3 counter. The counter runs at the rate of PWM clock. |

| 1    |      |             | The value ranges from 0 to $(2^32-1)$ .                                                                 |

### PWM\_PWM3\_PERIOD\_HPR

Address: Operational Base + offset (0x0034)

PWM Channel 3 Period Register/High Polarity Capture Register

| Bit | Attr | Reset Value | Description |

|-----|------|-------------|-------------|

|-----|------|-------------|-------------|

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                   |

|------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |      |             | PERIOD_LPR                                                                                                                                                                                                                                                                                                    |

|      |      |             | Output Waveform Period/Input Waveform<br>High Polarity Cycle                                                                                                                                                                                                                                                  |

| 31:0 | RW   | 0×00000000  | If PWM is operated at the continuous mode or one-shot mode, this value defines the period of the output waveform. Note that, if the PWM is operated at the center-aligned mode, the period should be an even one, and therefore only the bit [31:1] is taken into account and bit [0] always considered as 0. |

|      |      |             | If PWM is operated at the capture mode, this value indicates the effective high polarity cycles of input waveform.                                                                                                                                                                                            |

|      |      |             | This value is based on the PWM clock. The value ranges from 0 to $(2^32-1)$ .                                                                                                                                                                                                                                 |

#### PWM\_PWM3\_DUTY\_LPR

Address: Operational Base + offset (0x0038)

PWM Channel 3 Duty Register/Low Polarity Capture Register

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                    |

|------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | RW   | 0×00000000  | DUTY_LPR                                                                                                                                                                                                                                                                                                                       |

|      |      |             | Output Waveform Duty Cycle/Input<br>Waveform Low Polarity Cycle                                                                                                                                                                                                                                                                |

| 31:0 |      |             | If PWM is operated at the continuous mode or one-shot mode, this value defines the duty cycle of the output waveform. The PWM starts the output waveform with duty cycle. Note that, if the PWM is operated at the center-aligned mode, the period should be an even one, and therefore only the [31:1] is taken into account. |

|      |      |             | If PWM is operated at the capture mode, this value indicates the effective low polarity cycles of input waveform.                                                                                                                                                                                                              |

|      |      |             | This value is based on the PWM clock. The value ranges from 0 to (2^32-1).                                                                                                                                                                                                                                                     |

### PWM\_PWM3\_CTRL

Address: Operational Base + offset (0x003c)

## PWM Channel 3 Control Register

| Bit   | Attr | Reset Value | Description                                                                                                                                                                  |

|-------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |      |             | rpt                                                                                                                                                                          |

|       |      |             | Repeat Counter                                                                                                                                                               |

| 31:24 | RW   | 0×00        | This field defines the repeated effective periods of output waveform in one-shot mode. The value N means N+1 repeated effective periods.                                     |

|       |      |             | scale                                                                                                                                                                        |

|       |      |             | Scale Factor                                                                                                                                                                 |

| 23:16 | RW   | 0×00        | This fields defines the scale factor applied to prescaled clock. The value N means the clock is divided by 2*N. If N is 0, it means that the clock is divided by 512(2*256). |

| 15    | RO   | 0x0         | reserved                                                                                                                                                                     |

|       |      |             | prescale                                                                                                                                                                     |

|       |      | 0×0         | Prescale Factor                                                                                                                                                              |

| 14:12 | RW   |             | This field defines the prescale factor applied to input clock. The value N means that the input clock is divided by 2^N.                                                     |

| 11:10 | RO   | 0x0         | reserved                                                                                                                                                                     |

|       |      | •           | clk_sel                                                                                                                                                                      |

|       |      |             | Clock Source Select                                                                                                                                                          |

| 9     | RW   | 0×0         | 0: non-scaled clock is selected as PWM clock source. It means that the prescale clock is directly used as the PWM clock source                                               |

|       | C    |             | 1: scaled clock is selected as PWM clock source                                                                                                                              |

| 2     |      |             | lp_en                                                                                                                                                                        |

|       |      |             | Low Power Mode Enable                                                                                                                                                        |

|       |      |             | 0: disabled                                                                                                                                                                  |

| 8     | RW   | 0x0         | 1: enabled                                                                                                                                                                   |

|       |      |             | When PWM channel is inactive state and Low Power Mode is enabled, the path to PWM Clock prescale module is blocked to reduce power consumption.                              |

| 7:6   | RO   | 0x0         | reserved                                                                                                                                                                     |

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                 |  |

|-----|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5   | RW   | 0×0         | output_mode PWM Output mode 0: left aligned mode 1: center aligned mode                                                                                                                                                                                                                     |  |

| 4   | RW   | 0×0         | inactive_pol  Inactive State Output Polarity  This defines the output waveform polarity when PWM channel is in inactive state. The inactive state means that PWM finishes the complete waveform in one-shot mode or PWM channel is disabled.  0: negative  1: positive                      |  |

| 3   | RW   | 0×0         | duty_pol Duty Cycle Output Polarity This defines the polarity for duty cycle. PWM starts the output waveform with duty cycle. 0: negative 1: positive                                                                                                                                       |  |

| 2:1 | RW   | 0×0         | pwm_mode  PWM Operation Mode  00: One shot mode. PWM produces the waveform within the repeated times defined by PWMx_CTRL_rpt  01: Continuous mode. PWM produces the waveform continuously  10: Capture mode. PWM measures the cycles of high/low polarity of input waveform.  11: reserved |  |

| 0   | RW   | 0×0         | pwm_en PWM channel enable 0: disabled 1: enabled. If the PWM is worked the one-shot mode, this bit will be cleared at the end of operation                                                                                                                                                  |  |

## **PWM\_INTSTS**

Address: Operational Base + offset (0x0040)

Interrupt Status Register

| Bit     | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                             |  |

|---------|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:12   | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                |  |

|         |      | 0×0         | CH3_Pol                                                                                                                                                                                                                                                                                                                                                                                 |  |

|         |      |             | Channel 3 Interrupt Polarity Flag                                                                                                                                                                                                                                                                                                                                                       |  |

| 11      | RO   |             | This bit is used in capture mode in order to identify the transition of the input waveform when interrupt is generated. When bit is 1, please refer to PWM3_PERIOD_HPR to know the effective high cycle of Channel 0 input waveform. Otherwise, please refer to PWM3_PERIOD_HPR to know the effective low cycle of Channel 3 input waveform. Write 1 to CH3_IntSts will clear this bit. |  |

|         |      |             | CH2_Pol                                                                                                                                                                                                                                                                                                                                                                                 |  |

|         |      |             | Channel 2 Interrupt Polarity Flag                                                                                                                                                                                                                                                                                                                                                       |  |

| 10 RO ( |      | 0×0         | This bit is used in capture mode in order to identify the transition of the input waveform when interrupt is generated. When bit is 1, please refer to PWM2_PERIOD_HPR to know the effective high cycle of Channel 0 input waveform. Otherwise, please refer to PWM2_PERIOD_HPR to know the effective low cycle of Channel 2 input waveform. Write 1 to CH2_IntSts will clear this bit. |  |

|         | RO   | RO 0x0      | CH1_Pol                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 9       |      |             | Channel 1 Interrupt Polarity Flag                                                                                                                                                                                                                                                                                                                                                       |  |

|         |      |             | This bit is used in capture mode in order to identify the transition of the input waveform when interrupt is generated. When bit is 1, please refer to PWM1_PERIOD_HPR to know the effective high cycle of Channel 0 input waveform. Otherwise, please refer to PWM1_PERIOD_HPR to know the effective low cycle of Channel 1 input waveform. Write 1 to CH1_IntSts will clear this bit. |  |

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                             |  |

|-----|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     |      |             | CH0_Pol                                                                                                                                                                                                                                                                                                                                                                                 |  |

|     |      |             | Channel 0 Interrupt Polarity Flag                                                                                                                                                                                                                                                                                                                                                       |  |

| 8   | RO   | 0×0         | This bit is used in capture mode in order to identify the transition of the input waveform when interrupt is generated. When bit is 1, please refer to PWM0_PERIOD_HPR to know the effective high cycle of Channel 0 input waveform. Otherwise, please refer to PWM0_PERIOD_HPR to know the effective low cycle of Channel 0 input waveform. Write 1 to CH0_IntSts will clear this bit. |  |

| 7:4 | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                                                |  |

| 3   | RW   | 0×0         | CH3_IntSts Channel 3 Interrupt Status 0: Channel 3 Interrupt not generated 1: Channel 3 Interrupt generated                                                                                                                                                                                                                                                                             |  |

| 2   | RW   | 0×0         | CH2_IntSts Channel 2 Interrupt Status 0: Channel 2 Interrupt not generated 1: Channel 2 Interrupt generated                                                                                                                                                                                                                                                                             |  |

| 1   | RW   | 0x0         | CH1_IntSts Channel 1 Interrupt Status 0: Channel 1 Interrupt not generated 1: Channel 1 Interrupt generated                                                                                                                                                                                                                                                                             |  |

| 0   | RW   | 0x0         | CH0_IntSts Channel 0 Raw Interrupt Status 0: Channel 0 Interrupt not generated 1: Channel 0 Interrupt generated                                                                                                                                                                                                                                                                         |  |

## PWM\_INT\_EN

Address: Operational Base + offset (0x0044)

Interrupt Enable Register

| Bit  | Attr | Reset Value | Description |

|------|------|-------------|-------------|

| 31:4 | RO   | 0x0         | reserved    |

| Bit | Attr | Reset Value | Description                     |  |

|-----|------|-------------|---------------------------------|--|

|     |      |             | CH3_Int_en                      |  |

| 3   | RW   | 00          | Channel 3 Interrupt Enable      |  |

| 3   | KVV  | 0x0         | 0: Channel 3 Interrupt disabled |  |

|     |      |             | 1: Channel 3 Interrupt enabled  |  |

|     |      | 0×0         | CH2_Int_en                      |  |

| 2   | DVV  |             | Channel 2 Interrupt Enable      |  |

| 2   | RW   |             | 0: Channel 2 Interrupt disabled |  |

|     |      |             | 1: Channel 2 Interrupt enabled  |  |

|     |      | 0x0         | CH1_Int_en                      |  |

| 1   | DVV  |             | Channel 1 Interrupt Enable      |  |

| 1   | RW   |             | 0: Channel 1 Interrupt disabled |  |

|     |      |             | 1: Channel 1 Interrupt enabled  |  |

|     |      | 0×0         | CH0_Int_en                      |  |

| 0   | DVV  |             | Channel 0 Interrupt Enable      |  |

| 0   | RW   |             | 0: Channel 0 Interrupt disabled |  |

|     |      |             | 1: Channel 0 Interrupt enabled  |  |

# **36.5 Interface Description**

Table 36-1PWM Interface Description

| Module Pin | IO | Pad Name        | IOMUX Setting         |

|------------|----|-----------------|-----------------------|

| pwm3       | 0  | PWMirin_GPIO3d2 | GPIO3D_IOMUX[4]= 1'b1 |

| pwm2       | 0  | PWM2_GPIO0d4    | GPIO0D_IOMUX[8]= 1'b1 |

| pwm1       | 0  | PWM1_GPIO0d3    | GPIO0D_IOMUX[6]= 1'b1 |

| pwm0       | 0  | PWM0_GPIO0d2    | GPIO0D_IOMUX[4]= 1'b1 |

Notes: 1. I=input, O=output, I/O=input/output, bidirectional

2. There are two sets of IOs for each PWM channel

## **36.6 Application Notes**

### 36.6.1 PWM Reference Mode Standard Usage Flow