## **Chapter 28 I2S 2-channel**

### 28.1 Overview

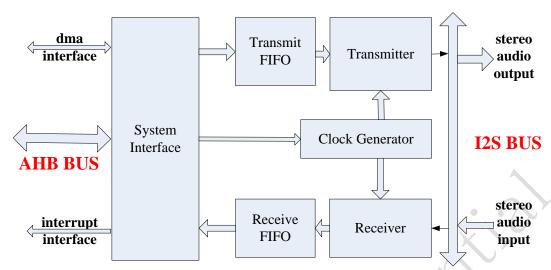

The I2S/PCM controller is designed for interfacing between the AHB bus and the I2S bus.

The I2S bus (Inter-IC sound bus) is a serial link for digital audio data transfer between devices in the system and is invented by Philips Semiconductor. Now it is widely used by many semiconductor manufacturers.

I2S bus is widely used in the devices such as ADC, DAC, DSP, CPU, etc. With the I2S interface, we can connect audio devices and the embedded SoC platform together and provide an audio interface solution for the system.

#### **28.1.1 Features**

Not only I2S but also PCM mode stereo audio output and input are supported in I2S/PCM1/2 controller.

- Support two internal 32-bit wide and 32-location deep FIFOs, one for transmitting and the other for receiving audio data

- Support AHB bus interface

- Support 16 ~ 32 bits audio data transfer

- Support master and slave mode

- Support DMA handshaking interface and configurable DMA water level

- Support transmit FIFO empty, underflow, receive FIFO full, overflow interrupt and all interrupts can be masked

- Support configurable water level of transmit FIFO empty and receive FIFO full interrupt

- Support combined interrupt output

- Support 2-channel audio transmitting in I2S mode and PCM mode

- Support 2-channel audio receiving in I2S and PCM mode

- Support up to 192kHz sample rate

- Support I2S normal, left and right justified mode serial audio data transfer

- Support PCM early, late1, late2, late3 mode serial audio data transfer

- Support MSB or LSB first serial audio data transfer

- Support 16 to 31 bit audio data left or right justified in 32-bit wide FIFO

- Support two 16-bit audio data store together in one 32-bit wide location

- Support 2 independent LRCK signals, one for receiving and the other for transmitting audio data

- Support configurable SCLK and LRCK polarity

- Support SCLK is equivalent to MCLK divided by an even number range from 2 to 64 in master mode

## 28.2 Block Diagram

Fig.28-1I2S/PCM1/2 controller (2 channel) Block Diagram

### **System Interface**

The system interface implements the AHB slave operation. It contains not only control registers of transmitters and receiver inside but also interrupt and DMA handshaking interface.

#### **Clock Generator**

The Clock Generator implements clock generation function. The input source clock to the module is MCLK\_I2S, and by the divider of the module, the clock generator generates SCLK and LRCK to transmitter and receiver.

### **Transmitters**

The Transmitters implement transmission operation. The transmitters can act as either a master or a slave, with I2S or PCM mode surround (up to 7.1 channel) serial audio interface.

#### Receiver

The Receiver implements receive operation. The receiver can act as either a master or a slave, with I2S or PCM mode stereo serial audio interface.

#### **Transmit FIFO**

The Transmit FIFO is the buffer to store transmitted audio data. The size of the FIFO is 32bits x 32.

### **Receive FIFO**

The Receive FIFO is the buffer to store received audio data. The size of the FIFO is 32bits x 32.

# 28.3 Function description

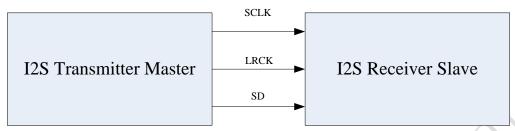

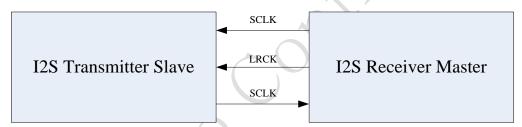

In the I2S/PCM1/2 controller, there are four types: transmitter-master & receiver-master; transmitter-master & receiver-slave; transmitter-slave & receiver-master; transmitter-slave & receiver-slave.

In broadcasting application, the I2S/PCM1/2 controller is used as a transmitter

and external or internal audio CODEC is used as a receiver. In recording application, the I2S/PCM1/2 controller is used as a receiver and external or internal audio CODEC is used as a transmitter. Either the I2S/PCM1/2 controller or the audio CODEC can act as a master or a slave, but if one is master, the other must be slave.

Fig.28-2I2S transmitter-master & receiver-slave condition

When the transmitter acts as a master, it sends all signals to thereceiver (the slave), and CPU controls when to send clock and data to the receiver. When acts as a slave, SD signal still goes from transmitter to receiver, but SCLK and LRCK signals are from the receiver (the master) to the transmitter. Based on three interface specifications, transmitting data should be ready before transmitter receives SCLK and LRCK signals. CPU should know when the receiver to initialize a transaction and when the transmitterto send data.

Fig.28-3I2S transmitter-slave & receiver-master condition

When the receiver acts as a master, it sends SCLK and LRCK signals to the transmitter (the slave) and receives serial data. So CPU must tell the transmitter when to start a transaction for it to prepare transmitting data then start a transfer and send clock and channel-select signals. When the receiver acts as a slave, CPU should only do initial setting and wait for all signals and then start reading data.

Before transmitting or receiving data, CPU need do initial setting to the I2S register. These includes CPU settings, I2S interface registers settings, and maybe the embedded SoC platform settings. These registers must be set before starting data transfer.

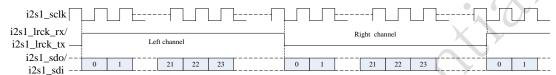

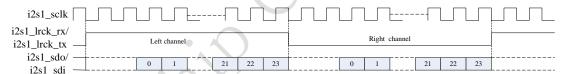

### 28.3.1 I2S normal mode

This is the waveform of I2S normal mode. For LRCK (i2s1\_lrck\_rx/i2s1\_lrck\_tx) signal, it goes low to indicate left channel and high to right channel. For SD (i2s1\_sdo, i2s1\_sdi) signal, it starts sending the first bit (MSB or LSB) one SCLK clock cycle after LRCK changes. The range of SD signal width is from 16 to 32bits.

Fig.28-4I2S normal mode timing format

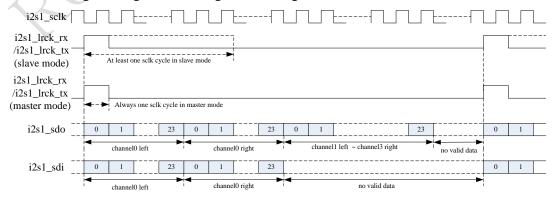

## 28.3.2 I2S left justified mode

This is the waveform of I2S left justified mode. For LRCK (i2s1\_lrck\_rx / i2s1\_lrck\_tx) signal, it goes high to indicate left channel and low to right channel. For SD (i2s1\_sdo, i2s1\_sdi) signal, it starts sending the first bit (MSB or LSB) at the same time when LRCK changes. The range of SD signal width is from 16 to 32bits.

Fig.28-5I2S left justified mode timing format

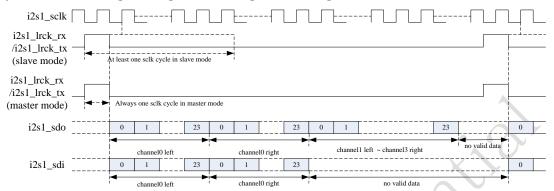

## 28.3.3 I2S right justified mode

This is the waveform of I2S right justified mode. For LRCK (i2s1\_lrck\_rx/i2s1\_lrck\_tx) signal, it goes high to indicate left channel and low to right channel. For SD (i2s1\_sdo, i2s1\_sdi) signal, it transfers MSB or LSB first; but what is different from I2S normal or left justified mode, the last bit of the transferred data is aligned to the transition edge of the LRCK signal while one bit is transferred at one SCLK cycle. The range of SD signal width is from 16 to 32bits.

Fig. 28-6I2S right justified mode timing format

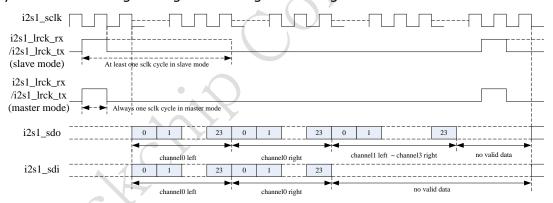

## 28.3.4 PCM early mode

This is the waveform of PCM early mode. For LRCK (i2s1\_lrck\_rx/i2s1\_lrck\_tx) signal, it goes high to indicate the start of a group of audio channels. For SD (i2s1\_sdo, i2s1\_sdi) signal, it sends the first bit (MSBor LSB) at the same time when LRCK goes high. The range of SD signal width is from 16 to 32bits.

Fig.28-7PCM early mode timing format

### 28.3.5 PCM late1 mode

This is the waveform of PCM early mode. For LRCK (i2s1\_lrck\_rx/i2s1\_lrck\_tx) signal, it goes high to indicate the start of a group of audio channels. For SD (i2s1\_sdo, i2s1\_sdi) signal, it sends the first bit (MSB or LSB) one SCLK clock cycle after LRCK goes high. The range of SD signal width is from 16 to 32bits.

Fig.28-8PCM late1 mode timing format

### 28.3.6 PCM late2 mode

This is the waveform of PCM early mode. For LRCK (i2s1\_lrck\_rx/i2s1\_lrck\_tx) signal, it goes high to indicate the start of a group of audio channels. For SD (i2s1\_sdo, i2s1\_sdi) signal, it sends the first bit (MSB or LSB)two SCLK clock cycles after LRCK goes high. The range of SD signal width is from 16 to 32bits.

Fig.28-9PCM late2 mode timing format

### 28.3.7 PCM late3 mode

This is the waveform of PCM early mode. For LRCK (i2s1\_lrck\_rx/i2s1\_lrck\_tx) signal, it goes high to indicate the start of a group of audio channels. For SD (i2s1\_sdo, i2s1\_sdi) signal, it sends the first bit (MSB or LSB) three SCLK clock cycles after LRCK goes high. The range of SD signal width is from 16 to 32bits.

Fig.28-10PCM late3 mode timing format

## 28.4 Register description

## 28.4.1 Register Summary

| Name        | Offset           | Size | Reset Value | Description                         |

|-------------|------------------|------|-------------|-------------------------------------|

| I2Sx_TXCR   | 0x0000           | W    | 0x0000000f  | transmit operation control register |

| I2Sx_RXCR   | 0x0004           | W    | 0x0000000f  | receive operation control register  |

| I2Sx_CKR    | 0x0008           | W    | 0x00071f1f  | clock generation register           |

| I2Sx_FIFOLR | 0x000c           | W    | 0x00000000  | FIFO level register                 |

| I2Sx_DMACR  | 0x0010           | W    | 0x001f0000  | DMA control register                |

| I2Sx_INTCR  | 0x0014           | W    | 0x00000000  | interrupt control register          |

| I2Sx_INTSR  | 0x0018           | W    | 0x00000000  | interrupt status register           |

| I2Sx_XFER   | 0x001c           | W    | 0x00000000  | Transfer Start Register             |

| I2Sx_CLR    | 0x0020           | W    | 0x00000000  | SCLK domain logic clear Register    |

| I2Sx_TXDR   | 0x0400<br>~0x7FC | W    | 0x00000000  | Transmit FIFO Data Register         |

| I2Sx_RXDR   | 0x0800<br>~0xBFC | W    | 0×00000000  | Receive FIFO Data Register          |

Notes: <u>Size</u>: **B**- Byte (8 bits) access, **HW**- Half WORD (16 bits) access, **W**-WORD (32 bits) access, x=1,2

# 28.4.2 Detail Register Description

## I2Sx\_TXCR

Address: Operational Base + offset (0x0000)

transmit operation control register

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                         |

|-------|------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:23 | RO   | 0x0         | reserved                                                                                                                                                                                                            |

| 22:17 | RW   | 0×00        | RCNT right justified counter (Can be written only when XFER[0] bit is 0.) Only valid in I2S Right justified format and slave tx mode is selected. Start to transmit data RCNT sclk cycles after left channel valid. |

| 16:15 | RW   | 0x0         | CSR<br>Channel select register<br>Must be 2'b00.                                                                                                                                                                    |

| Bit  | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                 |

|------|------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | RW   | 0×0         | HWT Halfword word transform (Can be written only when XFER[0] bit is 0.) Only valid when VDW select 16bit data. 0:32 bit data valid from AHB/APB bus. Low 16 bit for left channel and high 16 bit for right channel. 1:low 16bit data valid from AHB/APB bus, high 16 bit data invalid.                                                                     |

| 13   | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                    |

| 12   | RW   | 0×0         | SJM Store justified mode (Can be written only when XFER[0] bit is 0.) 16bit~31bit DATA stored in 32 bits width fifo. If VDW select 16bit data, this bit is valid only when HWT select 0.Because if HWT is 1, every fifo unit contain two 16bit data and 32 bit space is full, it is impossible to choose justified mode. 0:right justified 1:left justified |

| 11   | RW   | 0×0         | FBM First Bit Mode (Can be written only when XFER[0] bit is 0.) 0:MSB 1:LSB                                                                                                                                                                                                                                                                                 |

| 10:9 | RW   | 0x0         | IBM I2S bus mode (Can be written only when XFER[0] bit is 0.) 0:I2S normal 1:I2S Left justified 2:I2S Right justified 3:reserved                                                                                                                                                                                                                            |

| 8:7  | RW   | 0×0         | PBM PCM bus mode (Can be written only when XFER[0] bit is 0.) 0:PCM no delay mode 1:PCM delay 1 mode 2:PCM delay 2 mode 3:PCM delay 3 mode                                                                                                                                                                                                                  |

| 6    | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                    |

| 5    | RW   | 0x0         | TFS Transfer format select (Can be written only when XFER[0] bit is 0.) 0: I2S format 1: PCM format                                                                                                                                                                                                                                                         |

| Bit | Attr | Reset Value | Description                                                                                                                                                        |

|-----|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4:0 | RW   | 0x0f        | VDW Valid Data width (Can be written only when XFER[0] bit is 0.) 0~14:reserved 15:16bit 16:17bit 17:18bit 18:19bit n:(n+1)bit 28:29bit 29:30bit 30:31bit 31:32bit |

## I2Sx\_RXCR

Address: Operational Base + offset (0x0004)

receive operation control register

| receive | operation | n control registe |                                                                                                                                                                                                                                                                                                                                                             |

|---------|-----------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit     | Attr      | Reset Value       | Description                                                                                                                                                                                                                                                                                                                                                 |

| 31:15   | RO        | 0x0               | reserved                                                                                                                                                                                                                                                                                                                                                    |

| 14      | RW        | 0x0               | HWT Halfword word transform (Can be written only when XFER[1] bit is 0.) Only valid when VDW select 16bit data. 0:32 bit data valid to AHB/APB bus. Low 16 bit for left channel and high 16 bit for right channel. 1:low 16bit data valid to AHB/APB bus, high 16 bit data invalid.                                                                         |

| 13      | RO        | 0x0               | reserved                                                                                                                                                                                                                                                                                                                                                    |

| 12      | RW        | 0x0               | SJM Store justified mode (Can be written only when XFER[1] bit is 0.) 16bit~31bit DATA stored in 32 bits width fifo. If VDW select 16bit data, this bit is valid only when HWT select 0.Because if HWT is 1, every fifo unit contain two 16bit data and 32 bit space is full, it is impossible to choose justified mode. 0:right justified 1:left justified |

| 11      | RW        | 0x0               | FBM First Bit Mode (Can be written only when XFER[1] bit is 0.) 0:MSB 1:LSB                                                                                                                                                                                                                                                                                 |

| Bit  | Attr | Reset Value | Description                                                                                                                                                        |

|------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10:9 | RW   | 0x0         | IBM I2S bus mode (Can be written only when XFER[1] bit is 0.) 0:I2S normal 1:I2S Left justified 2:I2S Right justified 3:reserved                                   |

| 8:7  | RW   | 0×0         | PBM PCM bus mode (Can be written only when XFER[1] bit is 0.) 0:PCM no delay mode 1:PCM delay 1 mode 2:PCM delay 2 mode 3:PCM delay 3 mode                         |

| 6    | RO   | 0x0         | reserved                                                                                                                                                           |

| 5    | RW   | 0×0         | TFS Transfer format select (Can be written only when XFER[1] bit is 0.) 0:i2s 1:pcm                                                                                |

| 4:0  | RW   | 0x0f        | VDW Valid Data width (Can be written only when XFER[1] bit is 0.) 0~14:reserved 15:16bit 16:17bit 17:18bit 18:19bit n:(n+1)bit 28:29bit 29:30bit 30:31bit 31:32bit |

## I2Sx\_CKR

Address: Operational Base + offset (0x0008)

clock generation register

| sio sity genter a arrow i o greece. |      |                    |                                      |  |

|-------------------------------------|------|--------------------|--------------------------------------|--|

| Bit                                 | Attr | Reset Value        | Description                          |  |

| 31:28                               | RO   | 0x0                | reserved                             |  |

|                                     |      | MSS                |                                      |  |

|                                     |      |                    | Master/slave mode select             |  |

| 27                                  | RW   |                    | (Can be written only when XFER[1] or |  |

| 27   KW                             | UXU  | XFER[0] bit is 0.) |                                      |  |

|                                     |      |                    | 0:master mode(sclk output)           |  |

|                                     |      |                    | 1:slave mode(sclk input)             |  |

| Bit | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26  | RW   | 0x0         | CKP Sclk polarity (Can be written only when XFER[1] or XFER[0] bit is 0.) 0: sample data at posedgesclk and drive data at negedge sclk 1: sample data at negedge sclk and drive data at posedgesclk                                                                                                                                                                                                                                        |

| 25  | RW   | 0x0         | RLP Receive Irck polarity (Can be written only when XFER[1] or XFER[0] bit is 0.) 0:normal polarity (I2S normal: low for left channel, high for right channel I2S left/right just: high for left channel, low for right channel PCM start signal: high valid) 1:oppsite polarity (I2S normal: high for left channel, low for right channel I2S left/right just: low for left channel, high for right channel PCM start signal: low valid)  |

| 24  | RW   | 0x0         | TLP Transmit lrck polarity (Can be written only when XFER[1] or XFER[0] bit is 0.) 0:normal polarity (I2S normal: low for left channel, high for right channel I2S left/right just: high for left channel, low for right channel PCM start signal: high valid) 1:oppsite polarity (I2S normal: high for left channel, low for right channel I2S left/right just: low for left channel, high for right channel PCM start signal: low valid) |

| Bit              | Attr        | Reset Value       | Description                                                                                                                                                                                                                             |

|------------------|-------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Bit</b> 23:16 | <b>Attr</b> | Reset Value  0x07 | MDIV mclk divider (Can be written only when XFER[1] or XFER[0] bit is 0.) Serial Clock Divider = Fmclk / Ftxsclk-1.(mclkfrequecy / txsclk frequecy-1) 0 :Fmclk=Ftxsclk; 1 :Fmclk=2*Ftxsclk; 2,3 :Fmclk=4*Ftxsclk; 4,5 :Fmclk=6*Ftxsclk; |

|                  |             |                   | <br>2n,2n+1:Fmclk=(2n+2)*Ftxsclk;<br><br>60,61:Fmclk=62*Ftxsclk;<br>62,63:Fmclk=64*Ftxsclk;<br><br>252,253:Fmclk=254*Ftxsclk;<br>254,255:Fmclk=256*Ftxsclk;                                                                             |

| 15:8             | RW          | 0x1f              | RSD Receive sclk divider (Can be written only when XFER[1] or XFER[0] bit is 0.) Receive sclk divider= Fsclk/Frxlrck 0~30:reserved 31: 32fs 32: 33fs 33: 34fs 34: 35fs n: (n+1)fs 253: 254fs 254: 255fs 255: 256fs                      |

| 7:0              | RW          | 0x1f              | TSD Transmit sclk divider (Can be written only when XFER[1] or XFER[0] bit is 0.) Transmit sclk divider=Ftxsclk/Ftxlrck 0~30:reserved 31: 32fs 32: 33fs 33: 34fs 34: 35fs                                                               |

|                  |             |                   | n: (n+1)fs<br><br>253: 254fs<br>254: 255fs<br>255: 256fs                                                                                                                                                                                |

## I2Sx\_FIFOLR

Address: Operational Base + offset (0x000c)

FIFO level register

| Bit   | Attr | Reset Value | Description                                  |

|-------|------|-------------|----------------------------------------------|

| 31:30 | RO   | 0x0         | reserved                                     |

|       |      |             | RFL                                          |

| 29:24 | RO   | 0x00        | Receive FIFO Level                           |

| 29.24 | RU   | UXUU        | Contains the number of valid data entries in |

|       |      |             | the receive FIFO.                            |

| 23:6  | RO   | 0x0         | reserved                                     |

|       |      |             | TFL                                          |

| 5:0   | DO.  | 20 10200 1  | Transmit FIFO Level                          |

|       | KU   |             | Contains the number of valid data entries in |

|       |      |             | the transmit FIFO0.                          |

## I2Sx\_DMACR

Address: Operational Base + offset (0x0010)

DMA control register

| Bit   | Attr | Reset Value | Description                                                                                                                                                                                                                                                                                                                                                        |

|-------|------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:25 | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                           |

| 24    | RW   | 0x0         | RDE Receive DMA Enable 0 : Receive DMA disabled 1 : Receive DMA enabled                                                                                                                                                                                                                                                                                            |

| 23:21 | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                           |

| 20:16 | RW   | 0x1f        | RDL Receive Data Level This bit field controls the level at which a DMA request is made by the receive logic. The watermark level = DMARDL+1; that is, dma_rx_req is generated when the number of valid data entries in the receive FIFO is equal to or above this field value + 1.                                                                                |

| 15:9  | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                           |

| 8     | RW   | 0×0         | TDE Transmit DMA Enable 0: Transmit DMA disabled 1: Transmit DMA enabled                                                                                                                                                                                                                                                                                           |

| 7:5   | RO   | 0x0         | reserved                                                                                                                                                                                                                                                                                                                                                           |

| 4:0   | RW   | 0×00        | TDL Transmit Data Level This bit field controls the level at which a DMA request is made by the transmit logic. It is equal to the watermark level; that is, the dma_tx_req signal is generated when the number of valid data entries in the TXFIFO(TXFIFO0 if CSR=00;TXFIFO1 if CSR=01,TXFIFO2 if CSR=10,TXFIFO3 if CSR=11)is equal to or below this field value. |

## I2Sx\_INTCR

Address: Operational Base + offset (0x0014)

interrupt control register

|       |      | l register  |                                               |

|-------|------|-------------|-----------------------------------------------|

| Bit   | Attr | Reset Value | Description                                   |

| 31:25 | RO   | 0x0         | reserved                                      |

|       |      |             | RFT                                           |

|       |      |             | Receive FIFO Threshold                        |

| 24:20 | RW   | 0x00        | When the number of receive FIFO entries is    |

|       |      |             | more than or equal to this threshold plus 1,  |

|       |      |             | the receive FIFO full interrupt is triggered. |

| 19    | RO   | 0x0         | reserved                                      |

|       |      |             | RXOIC                                         |

| 18    | WO   | 0x0         | RX overrun interrupt clear                    |

|       |      |             | Write 1 to clear RX overrun interrupt.        |

|       |      |             | RXOIE                                         |

| 17    | RW   | 0×0         | RX overrun interrupt enable                   |

| 17    | I VV | UXU         | 0:disable                                     |

|       |      |             | 1:enable                                      |

|       |      |             | RXFIE                                         |

| 16    | RW   | 0x0         | RX full interrupt enable                      |

| 10    | IXVV | 0.00        | 0:disable                                     |

|       |      |             | 1:enable                                      |

| 15:9  | RO   | 0x0         | reserved                                      |

|       |      |             | TFT                                           |

|       |      |             | Transmit FIFO Threshold                       |

|       |      |             | When the number of transmit FIFO (TXFIFO0     |

| 8:4   | RW   | 0x00        | if CSR=00; TXFIFO1 if CSR=01, TXFIFO2 if      |

|       |      |             | CSR=10, TXFIFO3 if CSR=11) entries is less    |

|       |      |             | than or equal to this threshold, the transmit |

| _     |      |             | FIFO empty interrupt is triggered.            |

| 3     | RO   | 0x0         | reserved                                      |

|       |      |             | TXUIC                                         |

| 2     | WO   | 0x0         | TX underrun interrupt clear                   |

|       |      |             | Write 1 to clear TX underrun interrupt.       |

|       |      | A Y         | TXUIE                                         |

| 1     | RW   | 0x0         | TX underrun interrupt enable                  |

| _     | A.   | 1           | 0:disable                                     |

|       |      | <b>\</b>    | 1:enable                                      |

|       |      | 7           | TXEIE                                         |

| 0     | RW   | 0x0         | TX empty interrupt enable                     |

|       |      |             | 0:disable                                     |

|       |      |             | 1:enable                                      |

## I2Sx\_INTSR

Address: Operational Base + offset (0x0018)

interrupt status register

| Bit   | Attr | Reset Value | Description          |  |  |  |

|-------|------|-------------|----------------------|--|--|--|

| 31:18 | RO   | 0x0         | reserved             |  |  |  |

| 17    |      |             | RXOI                 |  |  |  |

|       | DO.  | 0.40        | RX overrun interrupt |  |  |  |

|       | RO   | 0x0         | 0:inactive           |  |  |  |

|       |      |             | 1:active             |  |  |  |

| Roc | 法<br>場<br>法<br>微<br>电子 | RK3 | 128 |

|-----|------------------------|-----|-----|

|     |                        |     |     |

|     |                        |     |     |

| Bit  | Attr | Reset Value | Description           |

|------|------|-------------|-----------------------|

|      |      |             | RXFI                  |

| 16   | RO   | 0×0         | RX full interrupt     |

| 10   | KO   | UXU         | 0:inactive            |

|      |      |             | 1:active              |

| 15:2 | RO   | 0x0         | reserved              |

|      |      |             | TXUI                  |

| 1    | RO   | 0×0         | TX underrun interrupt |

| 1    | KU   | UXU         | 0:inactive            |

|      |      |             | 1:active              |

|      |      |             | TXEI                  |

| 0    | RO   | 0×0         | TX empty interrupt    |

| U    | KO   | UXU         | 0:inactive            |

|      |      |             | 1:active              |

## I2Sx\_XFER

Address: Operational Base + offset (0x001c)

Transfer Start Register

| Bit  | Bit Attr Reset Value |     | Description                                                       |  |

|------|----------------------|-----|-------------------------------------------------------------------|--|

| 31:2 | RO                   | 0x0 | reserved                                                          |  |

| 1    | RW                   | 0×0 | RXS RX Transfer start bit 0:stop RX transfer. 1:start RX transfer |  |

| 0    | RW                   | 0×0 | TXS TX Transfer start bit 0:stop TX transfer. 1:start TX transfer |  |

## I2Sx\_CLR

Address: Operational Base + offset (0x0020)

SCLK domain logic clear Register

| Bit  | Attr | Reset Value | Description                                                                        |

|------|------|-------------|------------------------------------------------------------------------------------|

| 31:2 | RO   | 0x0         | reserved                                                                           |

| 1    | RW   | 0×0         | RXC RX logic clear This is a self cleard bit. Write 1 to clear all receive logic.  |

| 0    | RW   | 0×0         | TXC TX logic clear This is a self cleard bit. Write 1 to clear all transmit logic. |

## I2Sx\_TXDR

Address: Operational Base + offset (0x0024)

Transmit FIFO Data Register

| Rit Attr Reset Value Description | Dit Atti Reset value Description | Bit | Attr | <b>Reset Value</b> | Description |

|----------------------------------|----------------------------------|-----|------|--------------------|-------------|

|----------------------------------|----------------------------------|-----|------|--------------------|-------------|

| Bit  | Attr | Reset Value | Description                                                                                    |

|------|------|-------------|------------------------------------------------------------------------------------------------|

| 31:0 | WO   | 0x00000000  | TXDR Transmit FIFO Data Register When it is written to, data are moved into the transmit FIFO. |

## I2Sx\_RXDR

Address: Operational Base + offset (0x0028)

Receive FIFO Data Register

| Bit  | Attr | Reset Value | Description                                                                                      |

|------|------|-------------|--------------------------------------------------------------------------------------------------|

| 31:0 | RO   | 000000000   | RXDR Receive FIFO Data Register When the register is read, data in the receive FIFO is accessed. |

# 28.5 Interface description

I2S has 2 IOMUX, which controlled by GRF\_SOC\_CON1[5].

When GRF SOC\_CON1[5] is 1'b0, the IOMUX is as follow.

| <b>Module Pin</b> | Direction | Pad Name                                         | IOMUX Setting                |

|-------------------|-----------|--------------------------------------------------|------------------------------|

|                   | 1         | I2S                                              |                              |

| i2s_clk           | 0         | IO_I2Smclk<br>_MMC1clkou<br>t_XIN32k_G<br>PIO1a0 | GRF_GPIO1A_IOMUX[1: 0]=2'b1  |

| i2s_sclk          | I/O       | IO_I2Ssclk_<br>MMC1d0_PM<br>ICsleep1_GP<br>IO1a1 | GRF_GPIO1A_IOMUX[ 3:2]=2'b1  |

| i2s_lrck_rx       | I/O       | IO_I2Slrckr<br>x_MMC1d1_<br>GPIO1a2              | GRF_GPIO1A_IOMUX[ 5:4]=2'b1  |

| i2s_lrck_tx       | I/O       | IO_I2Slrcktx<br>_GPIO1a3                         | GRF_GPIO1A_IOMUX[ 6]=1'b1    |

| i2s_sdo           | 0         | IO_I2Ssdo_<br>MMC1d2_GP<br>IO1a4                 | GRF_GPIO1A_IOMUX[9:8]=2'b1   |

| i2s_sdi           | I         | IO_I2Ssdi_<br>MMC1d3_GP<br>IO1a5                 | GRF_GPIO1A_IOMUX[11:10]=2'b1 |

When GRF SOC CON1[5] is 1'b1, the IOMUX is as follow.

| Module Pin | Direction | Pad Name                            | IOMUX Setting                |  |

|------------|-----------|-------------------------------------|------------------------------|--|

| I2S        |           |                                     |                              |  |

| i2s_clk    | 0         | IO_I2S1mcl<br>k_GPIO0b0             | GRF_GPIO0B_IOMUX[ 0]=1'b1    |  |

| i2s_sclk   | I/O       | IO_I2S1sclk<br>_SPIclkm_G<br>PIO0b1 | GRF_GPIO0B _IOMUX[3:2]=2'b01 |  |

| i2s_lrck_rx | I/O | IO_I2S1lrck<br>rx_SPItxdm<br>_GPIO0b3 | GRF_GPIO0B _IOMUX[7:6]=2'b01  |

|-------------|-----|---------------------------------------|-------------------------------|

| i2s_lrck_tx | I/O | IO_I2S1lrck<br>tx_GPIO0b4             | GRF_GPIO0B _IOMUX[ 8]=1'b1    |

| i2s_sdo     | 0   | IO_I2S1sdo<br>_SPIrxdm_G<br>PIO0b5    | GRF_GPIO0B _IOMUX[11:10]=2'b1 |

| i2s_sdi     | I   | IO_I2S1sdi_<br>SPIcsn0m_<br>GPIO0b6   | GRF_GPIO0B _IOMUX[13:12]=1'b1 |

# 28.6 Application Notes

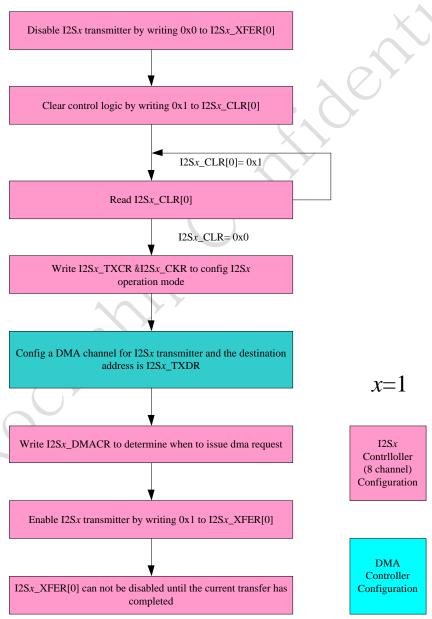

Fig.28-11I2S/PCM1/2 controller transmit operation flow chart

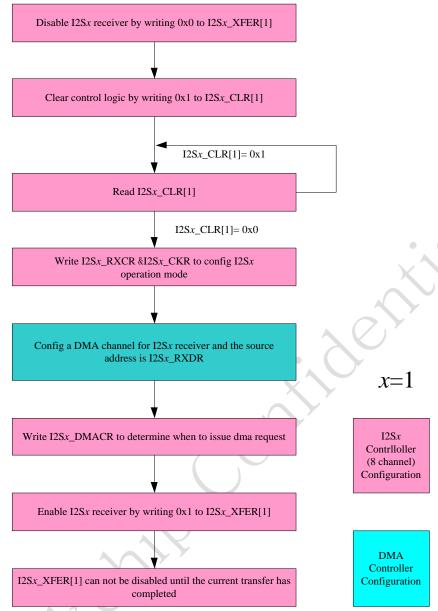

Fig.28-12I2S/PCM1/2 controller receive operation flow chart